SPRS292A − OCTOBER 2005 − REVISED NOVEMBER 2005

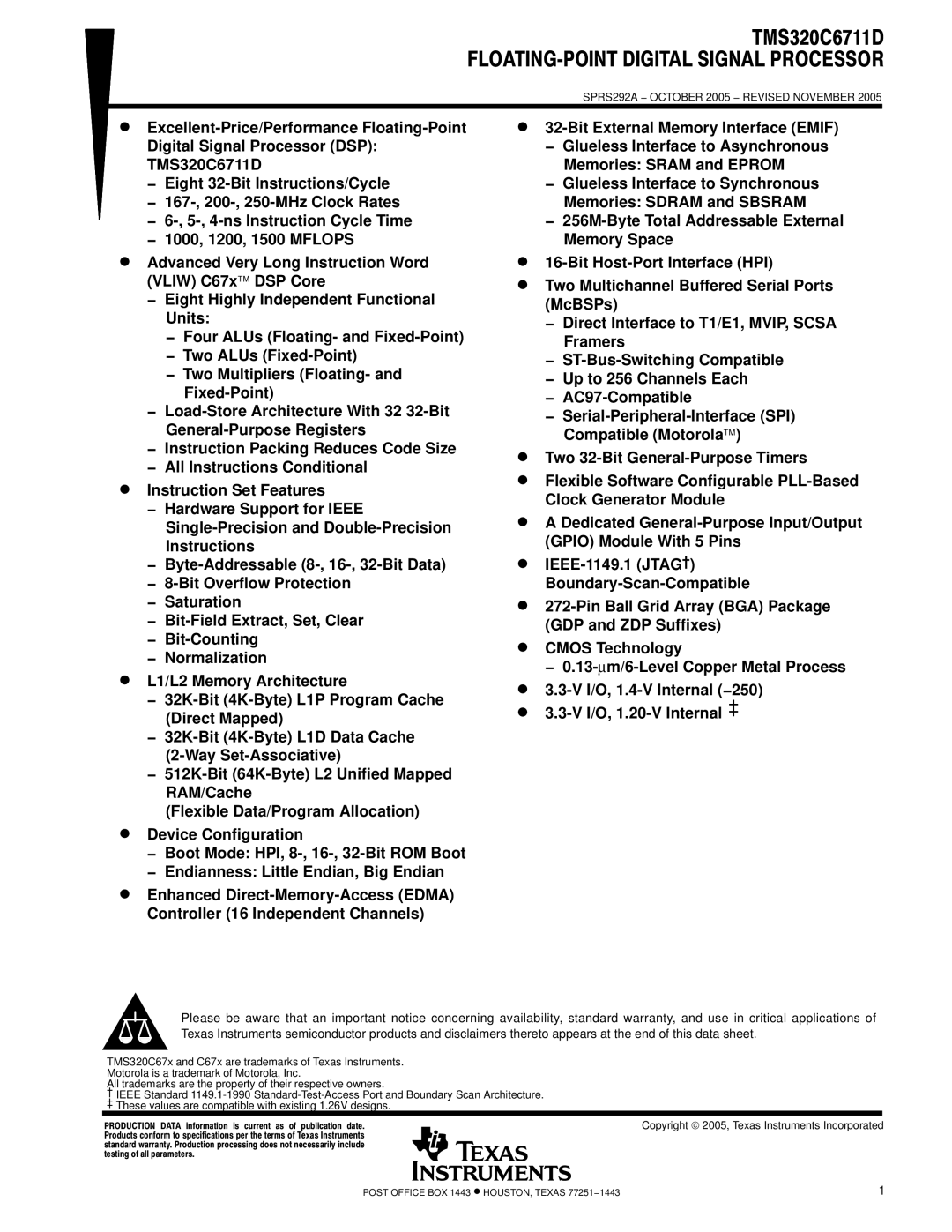

D

−Eight

−

−

−1000, 1200, 1500 MFLOPS

DAdvanced Very Long Instruction Word (VLIW) C67x DSP Core

−Eight Highly Independent Functional Units:

−Four ALUs (Floating- and

−Two ALUs

−Two Multipliers (Floating- and

−

−Instruction Packing Reduces Code Size

−All Instructions Conditional

DInstruction Set Features

− Hardware Support for IEEE

−

−

−Saturation

−

−

−Normalization

DL1/L2 Memory Architecture

−

−

−

(Flexible Data/Program Allocation)

DDevice Configuration

−Boot Mode: HPI,

−Endianness: Little Endian, Big Endian

DEnhanced

D

−Glueless Interface to Asynchronous Memories: SRAM and EPROM

−Glueless Interface to Synchronous Memories: SDRAM and SBSRAM

−

D

DTwo Multichannel Buffered Serial Ports (McBSPs)

−Direct Interface to T1/E1, MVIP, SCSA Framers

−

−Up to 256 Channels Each

−

−

DTwo

DFlexible Software Configurable

DA Dedicated

D

D

DCMOS Technology

−0.13-

D

D

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

TMS320C67x and C67x are trademarks of Texas Instruments.

Motorola is a trademark of Motorola, Inc.

All trademarks are the property of their respective owners.

†IEEE Standard

‡ These values are compatible with existing 1.26V designs.

Copyright 2005, Texas Instruments Incorporated

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251−1443 | 1 |