SPRS292A − OCTOBER 2005 − REVISED NOVEMBER 2005

peripheral register descriptions (continued)

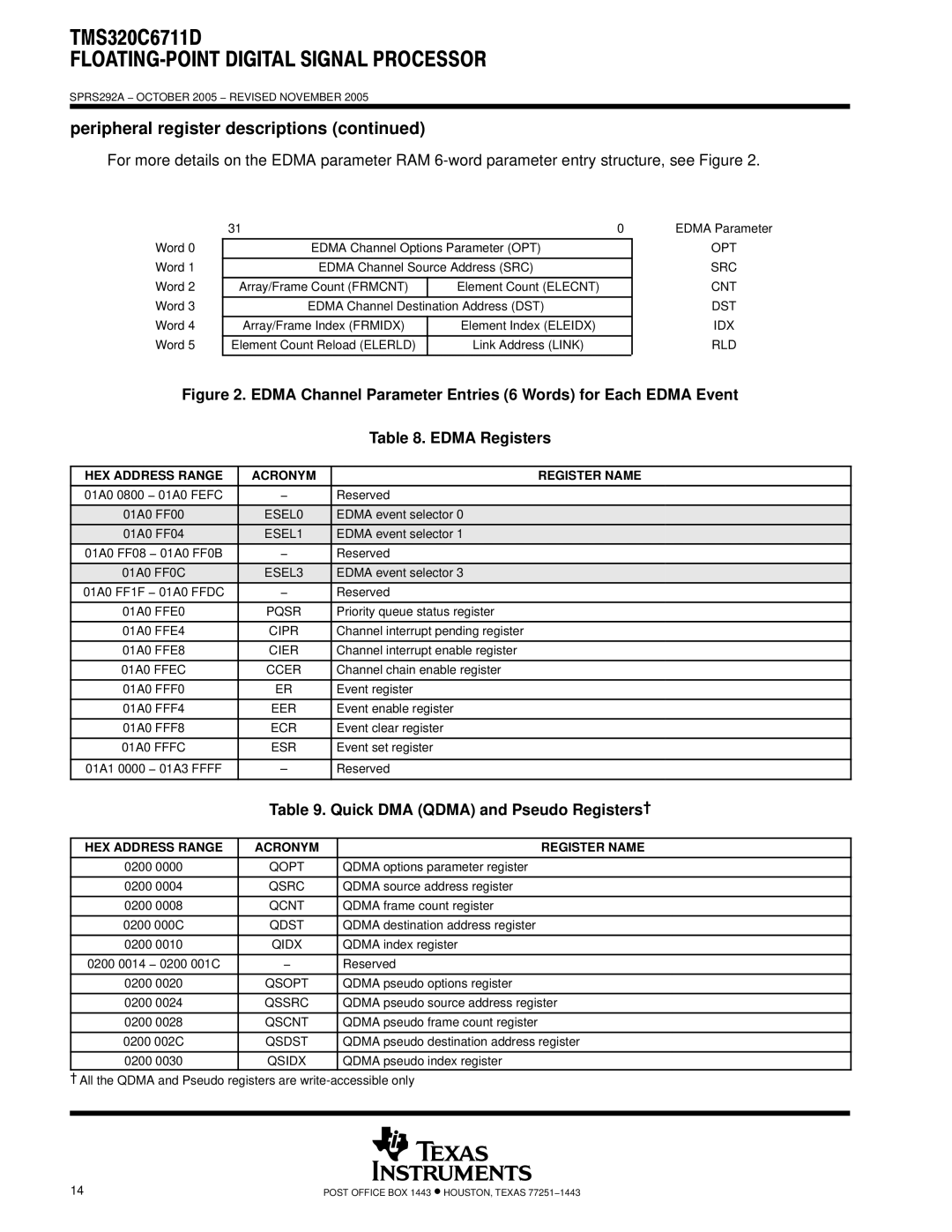

For more details on the EDMA parameter RAM

Word 0

Word 1

Word 2

Word 3

Word 4

Word 5

310

EDMA Channel Options Parameter (OPT)

EDMA Channel Source Address (SRC)

Array/Frame Count (FRMCNT) | Element Count (ELECNT) |

|

|

EDMA Channel Destination Address (DST) | |

|

|

Array/Frame Index (FRMIDX) | Element Index (ELEIDX) |

|

|

Element Count Reload (ELERLD) | Link Address (LINK) |

|

|

EDMA Parameter

OPT

SRC

CNT

DST

IDX

RLD

Figure 2. EDMA Channel Parameter Entries (6 Words) for Each EDMA Event | |||

|

|

| Table 8. EDMA Registers |

|

|

|

|

HEX ADDRESS RANGE | ACRONYM |

| REGISTER NAME |

|

|

|

|

01A0 0800 − 01A0 FEFC | − | Reserved | |

|

|

|

|

01A0 FF00 | ESEL0 | EDMA event selector 0 | |

01A0 FF04 | ESEL1 | EDMA event selector 1 | |

01A0 FF08 − 01A0 FF0B | − | Reserved | |

|

|

|

|

01A0 FF0C | ESEL3 | EDMA event selector 3 | |

01A0 FF1F − 01A0 FFDC | − | Reserved | |

|

|

|

|

01A0 FFE0 | PQSR | Priority queue status register | |

|

|

|

|

01A0 FFE4 | CIPR | Channel interrupt pending register | |

|

|

|

|

01A0 FFE8 | CIER | Channel interrupt enable register | |

|

|

|

|

01A0 FFEC | CCER | Channel chain enable register | |

|

|

|

|

01A0 FFF0 | ER | Event register | |

|

|

|

|

01A0 FFF4 | EER | Event enable register | |

|

|

|

|

01A0 FFF8 | ECR | Event clear register | |

|

|

|

|

01A0 FFFC | ESR | Event set register | |

|

|

|

|

01A1 0000 − 01A3 FFFF | – | Reserved | |

|

|

|

|

| Table 9. Quick DMA (QDMA) and Pseudo Registers† | ||

|

|

|

|

HEX ADDRESS RANGE | ACRONYM |

| REGISTER NAME |

|

|

|

|

0200 0000 | QOPT |

| QDMA options parameter register |

|

|

|

|

0200 0004 | QSRC |

| QDMA source address register |

|

|

|

|

0200 0008 | QCNT |

| QDMA frame count register |

|

|

|

|

0200 000C | QDST |

| QDMA destination address register |

|

|

|

|

0200 0010 | QIDX |

| QDMA index register |

|

|

|

|

0200 0014 − 0200 001C | − |

| Reserved |

|

|

|

|

0200 0020 | QSOPT |

| QDMA pseudo options register |

|

|

|

|

0200 0024 | QSSRC |

| QDMA pseudo source address register |

|

|

|

|

0200 0028 | QSCNT |

| QDMA pseudo frame count register |

|

|

|

|

0200 002C | QSDST |

| QDMA pseudo destination address register |

|

|

|

|

0200 0030 | QSIDX |

| QDMA pseudo index register |

†All the QDMA and Pseudo registers are

14 | POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251−1443 |