SPRS292A − OCTOBER 2005 − REVISED NOVEMBER 2005

EMIF device speed

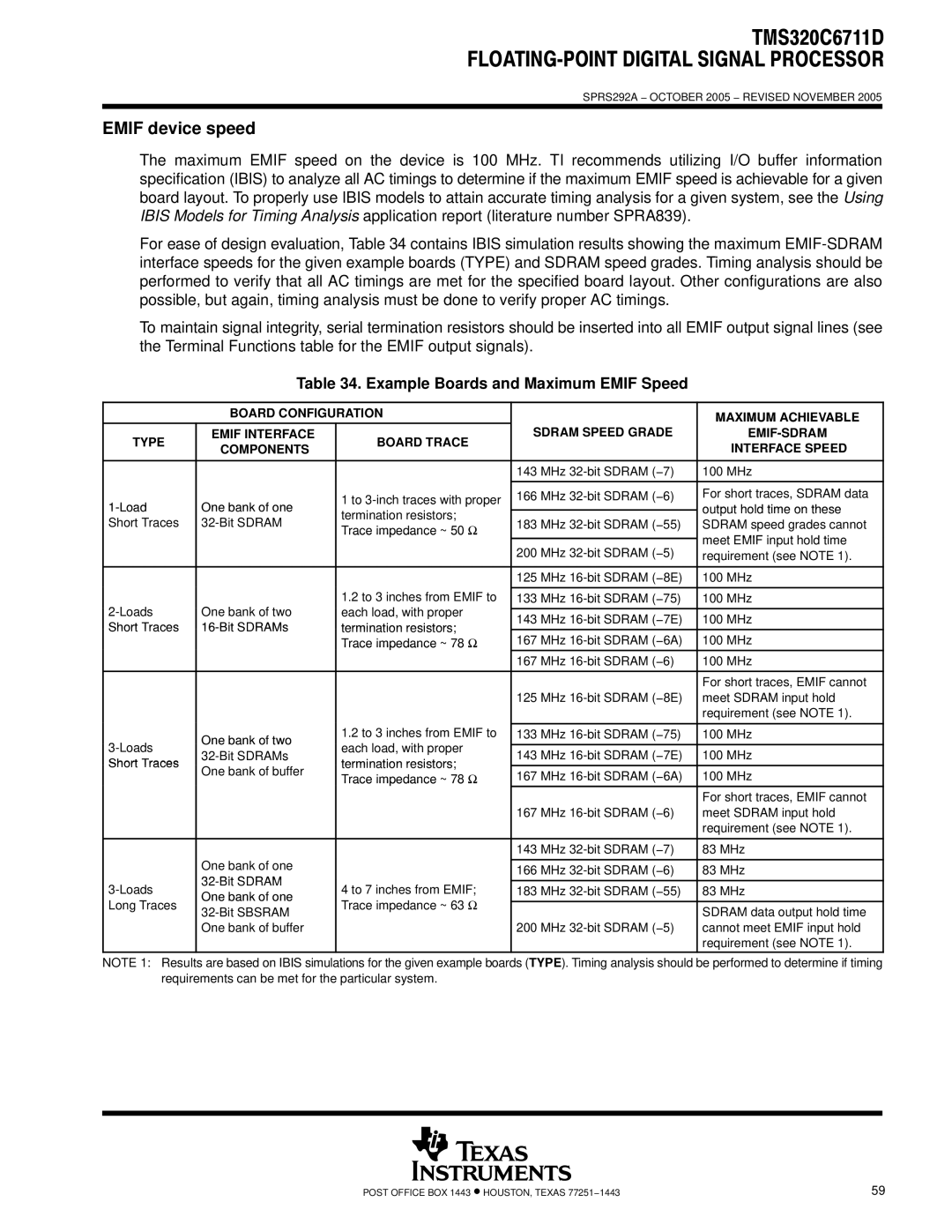

The maximum EMIF speed on the device is 100 MHz. TI recommends utilizing I/O buffer information specification (IBIS) to analyze all AC timings to determine if the maximum EMIF speed is achievable for a given board layout. To properly use IBIS models to attain accurate timing analysis for a given system, see the Using IBIS Models for Timing Analysis application report (literature number SPRA839).

For ease of design evaluation, Table 34 contains IBIS simulation results showing the maximum

To maintain signal integrity, serial termination resistors should be inserted into all EMIF output signal lines (see the Terminal Functions table for the EMIF output signals).

Table 34. Example Boards and Maximum EMIF Speed

| BOARD CONFIGURATION |

| MAXIMUM ACHIEVABLE | ||

|

|

|

| ||

TYPE | EMIF INTERFACE | BOARD TRACE | SDRAM SPEED GRADE | ||

COMPONENTS |

| INTERFACE SPEED | |||

|

|

| |||

|

|

|

|

| |

|

|

| 143 MHz | 100 MHz | |

|

|

|

|

| |

One bank of one | 1 to | 166 MHz | For short traces, SDRAM data | ||

| output hold time on these | ||||

termination resistors; |

| ||||

| |||||

Short Traces | 183 MHz | SDRAM speed grades cannot | |||

Trace impedance ~ 50 Ω | |||||

|

|

| meet EMIF input hold time | ||

|

|

| 200 MHz | ||

|

|

| requirement (see NOTE 1). | ||

|

|

|

|

| |

|

|

| 125 MHz | 100 MHz | |

|

| 1.2 to 3 inches from EMIF to |

|

| |

One bank of two | 133 MHz | 100 MHz | |||

each load, with proper |

|

| |||

143 MHz | 100 MHz | ||||

Short Traces | termination resistors; | ||||

|

| ||||

167 MHz | 100 MHz | ||||

|

| Trace impedance ~ 78 Ω | |||

|

|

| 167 MHz | 100 MHz | |

|

|

|

|

| |

|

|

|

| For short traces, EMIF cannot | |

|

|

| 125 MHz | meet SDRAM input hold | |

|

|

|

| requirement (see NOTE 1). | |

|

| 1.2 to 3 inches from EMIF to |

|

| |

One bank of two | 133 MHz | 100 MHz | |||

each load, with proper |

|

| |||

143 MHz | 100 MHz | ||||

Short Traces | termination resistors; | ||||

One bank of buffer |

|

| |||

167 MHz | 100 MHz | ||||

| Trace impedance ~ 78 Ω | ||||

|

| ||||

|

|

|

| For short traces, EMIF cannot | |

|

|

| 167 MHz | meet SDRAM input hold | |

|

|

|

| requirement (see NOTE 1). | |

|

|

|

|

| |

|

|

| 143 MHz | 83 MHz | |

| One bank of one |

|

|

| |

|

| 166 MHz | 83 MHz | ||

|

| ||||

4 to 7 inches from EMIF; |

|

| |||

183 MHz | 83 MHz | ||||

One bank of one | |||||

Long Traces | Trace impedance ~ 63 Ω |

|

| ||

| SDRAM data output hold time | ||||

|

|

| |||

| One bank of buffer |

| 200 MHz | cannot meet EMIF input hold | |

|

|

|

| requirement (see NOTE 1). | |

NOTE 1: Results are based on IBIS simulations for the given example boards (TYPE). Timing analysis should be performed to determine if timing requirements can be met for the particular system.

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251−1443 | 59 |