SPRS292A − OCTOBER 2005 − REVISED NOVEMBER 2005

power-down mode logic

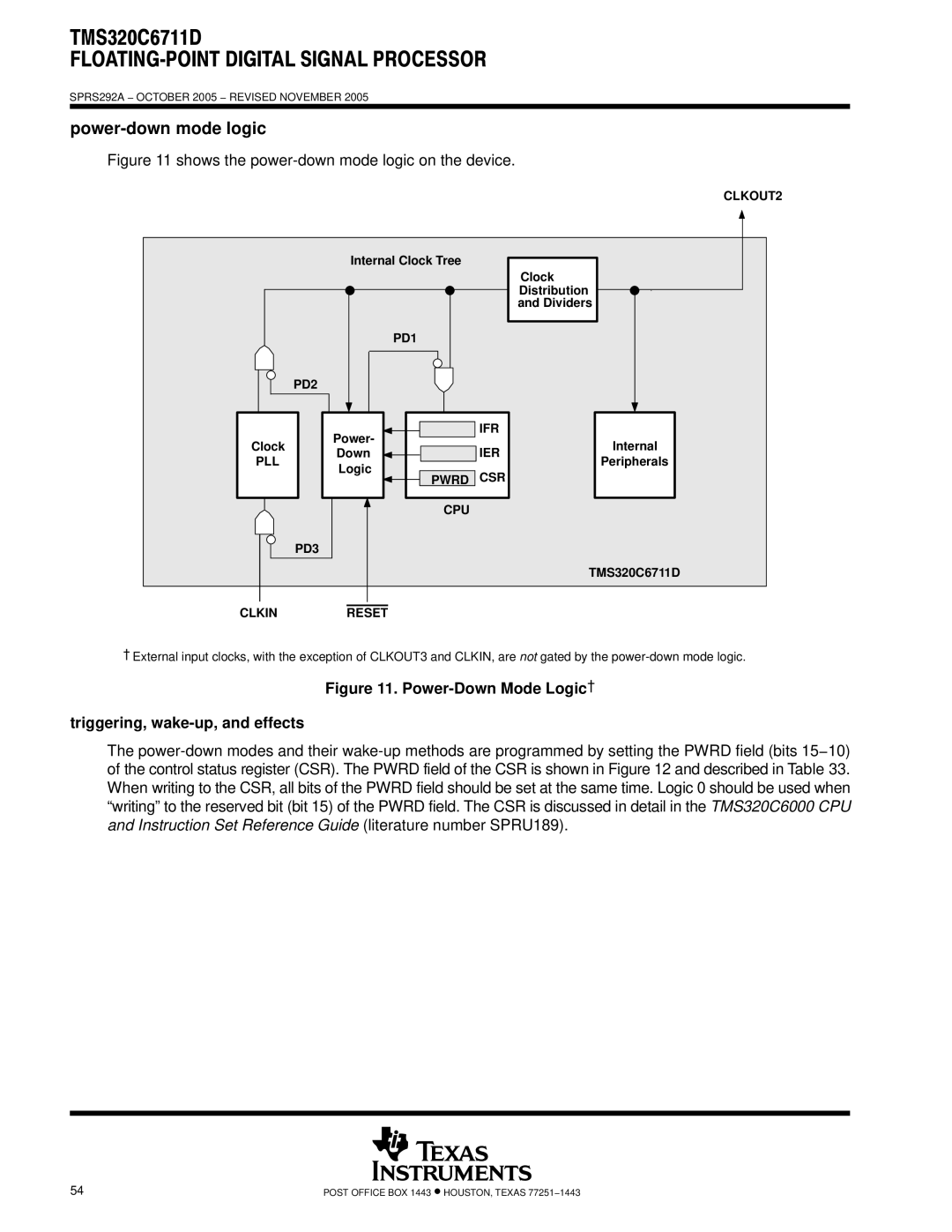

Figure 11 shows the power-down mode logic on the device.

CLKOUT2

Internal Clock Tree

PD1

PD2

Clock

Distribution

and Dividers

Clock |

PLL |

PD3

IFR

Power-

Down ![]()

![]()

![]() IER

IER

Logic

PWRD CSR

CPU

Internal

Peripherals

TMS320C6711D

CLKINRESET

†External input clocks, with the exception of CLKOUT3 and CLKIN, are not gated by the

Figure 11. Power-Down Mode Logic†

triggering, wake-up, and effects

The

54 | POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251−1443 |