SPRS292A − OCTOBER 2005 − REVISED NOVEMBER 2005

PARAMETER MEASUREMENT INFORMATION

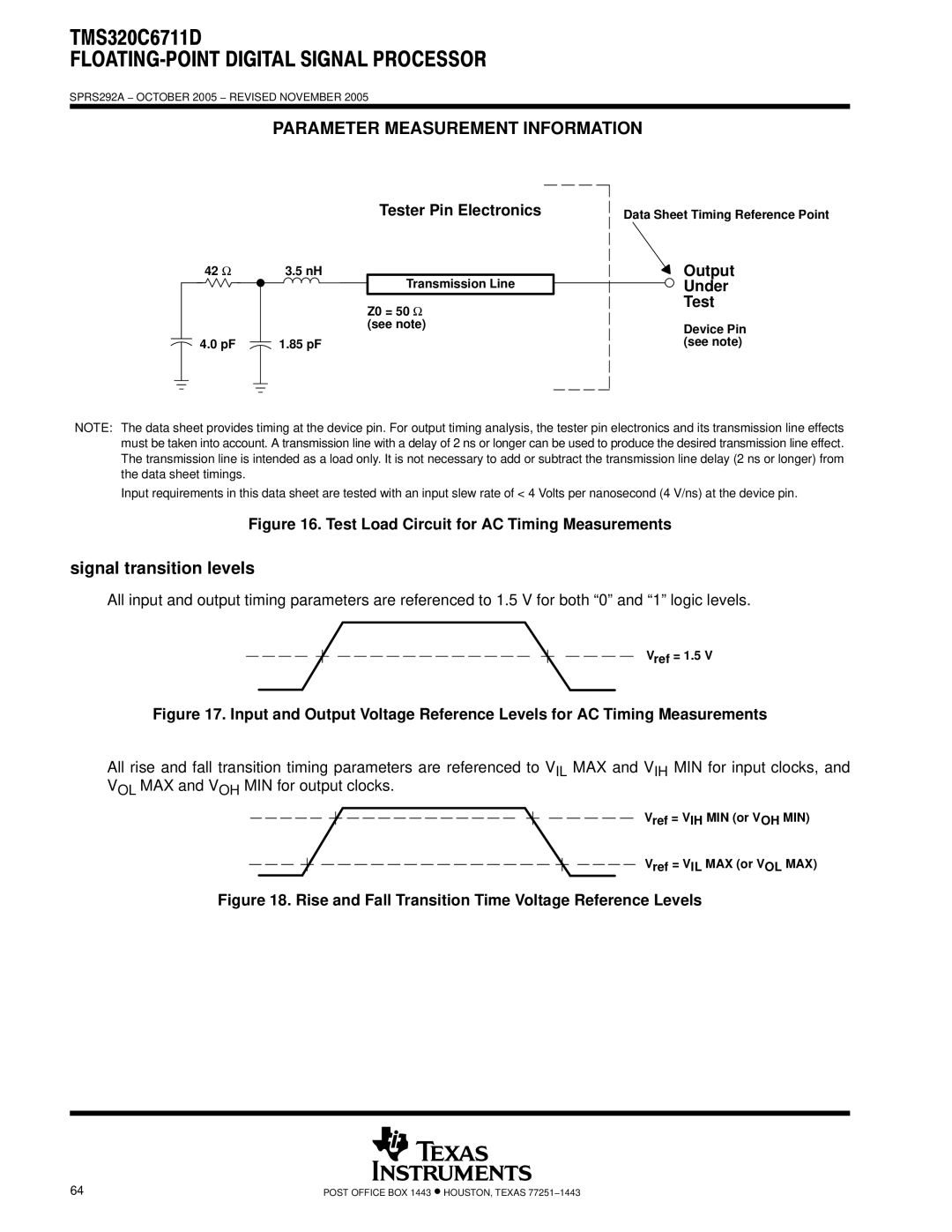

42 Ω | 3.5 nH |

|

|

4.0 pF | 1.85 pF |

Tester Pin Electronics

Transmission Line

Z0 = 50 Ω

(see note)

Data Sheet Timing Reference Point

Output

Under

Test

Device Pin (see note)

NOTE: The data sheet provides timing at the device pin. For output timing analysis, the tester pin electronics and its transmission line effects must be taken into account. A transmission line with a delay of 2 ns or longer can be used to produce the desired transmission line effect. The transmission line is intended as a load only. It is not necessary to add or subtract the transmission line delay (2 ns or longer) from the data sheet timings.

Input requirements in this data sheet are tested with an input slew rate of < 4 Volts per nanosecond (4 V/ns) at the device pin.

Figure 16. Test Load Circuit for AC Timing Measurements

signal transition levels

All input and output timing parameters are referenced to 1.5 V for both “0” and “1” logic levels.

Vref = 1.5 V

Figure 17. Input and Output Voltage Reference Levels for AC Timing Measurements

All rise and fall transition timing parameters are referenced to VIL MAX and VIH MIN for input clocks, and VOL MAX and VOH MIN for output clocks.

Vref = VIH MIN (or VOH MIN)

Vref = VIL MAX (or VOL MAX)

Figure 18. Rise and Fall Transition Time Voltage Reference Levels

64 | POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251−1443 |