SPRS292A − OCTOBER 2005 − REVISED NOVEMBER 2005

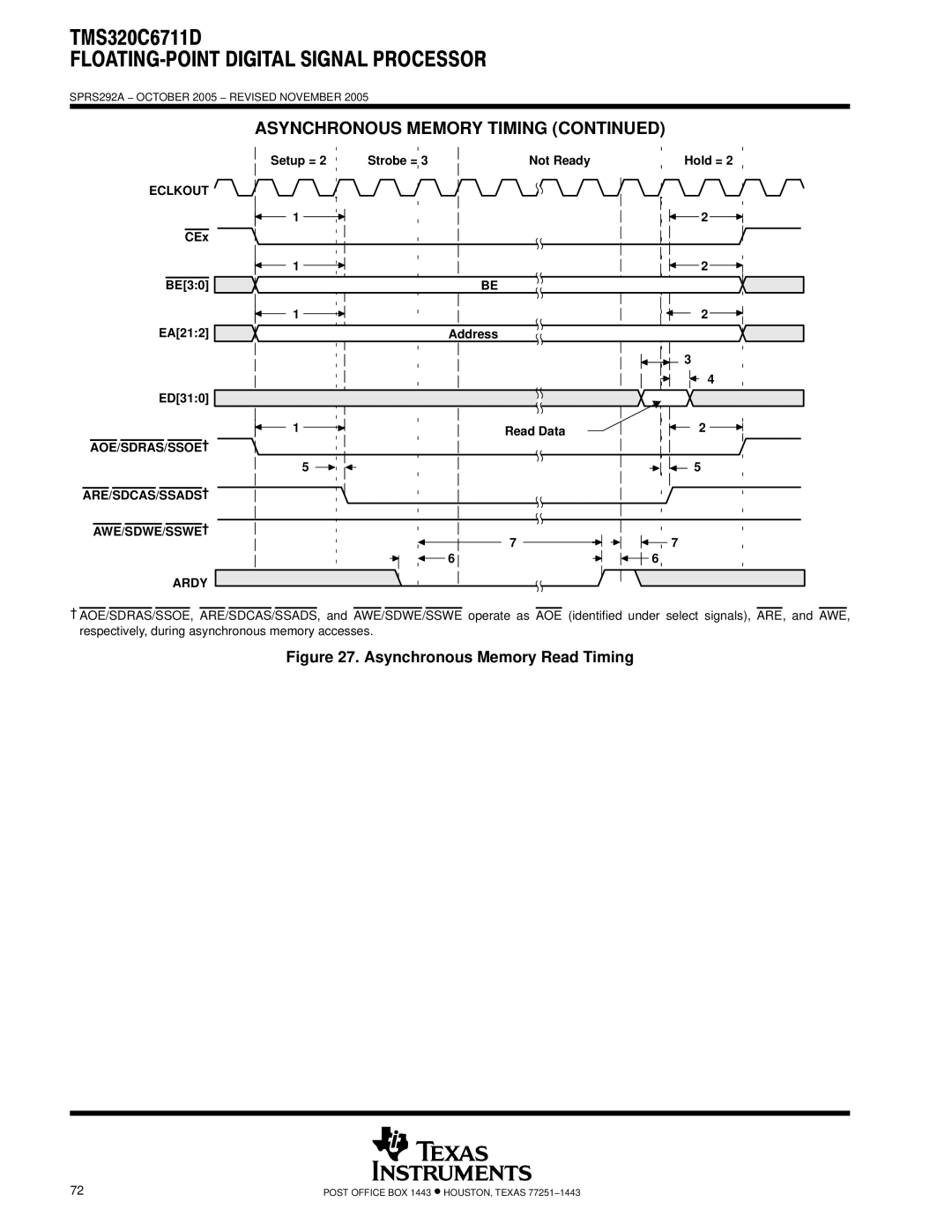

ASYNCHRONOUS MEMORY TIMING (CONTINUED)

Setup = 2 | Strobe = 3 | Not Ready | Hold = 2 |

ECLKOUT |

|

|

|

1 |

|

| 2 |

CEx |

|

|

|

1 |

|

| 2 |

BE[3:0] |

| BE |

|

1 |

|

| 2 |

EA[21:2] |

| Address |

|

|

|

| 3 |

|

|

| 4 |

ED[31:0] |

|

|

|

1 |

| Read Data | 2 |

AOE/SDRAS/SSOE† |

|

|

|

5 |

|

| 5 |

ARE/SDCAS/SSADS† |

|

|

|

AWE/SDWE/SSWE† |

| 7 | 7 |

|

| ||

|

| 6 | 6 |

ARDY |

|

|

|

†AOE/SDRAS/SSOE, ARE/SDCAS/SSADS, and AWE/SDWE/SSWE operate as AOE (identified under select signals), ARE, and AWE, respectively, during asynchronous memory accesses.

Figure 27. Asynchronous Memory Read Timing

72 | POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251−1443 |