SPRS292A − OCTOBER 2005 − REVISED NOVEMBER 2005

|

|

|

|

|

|

|

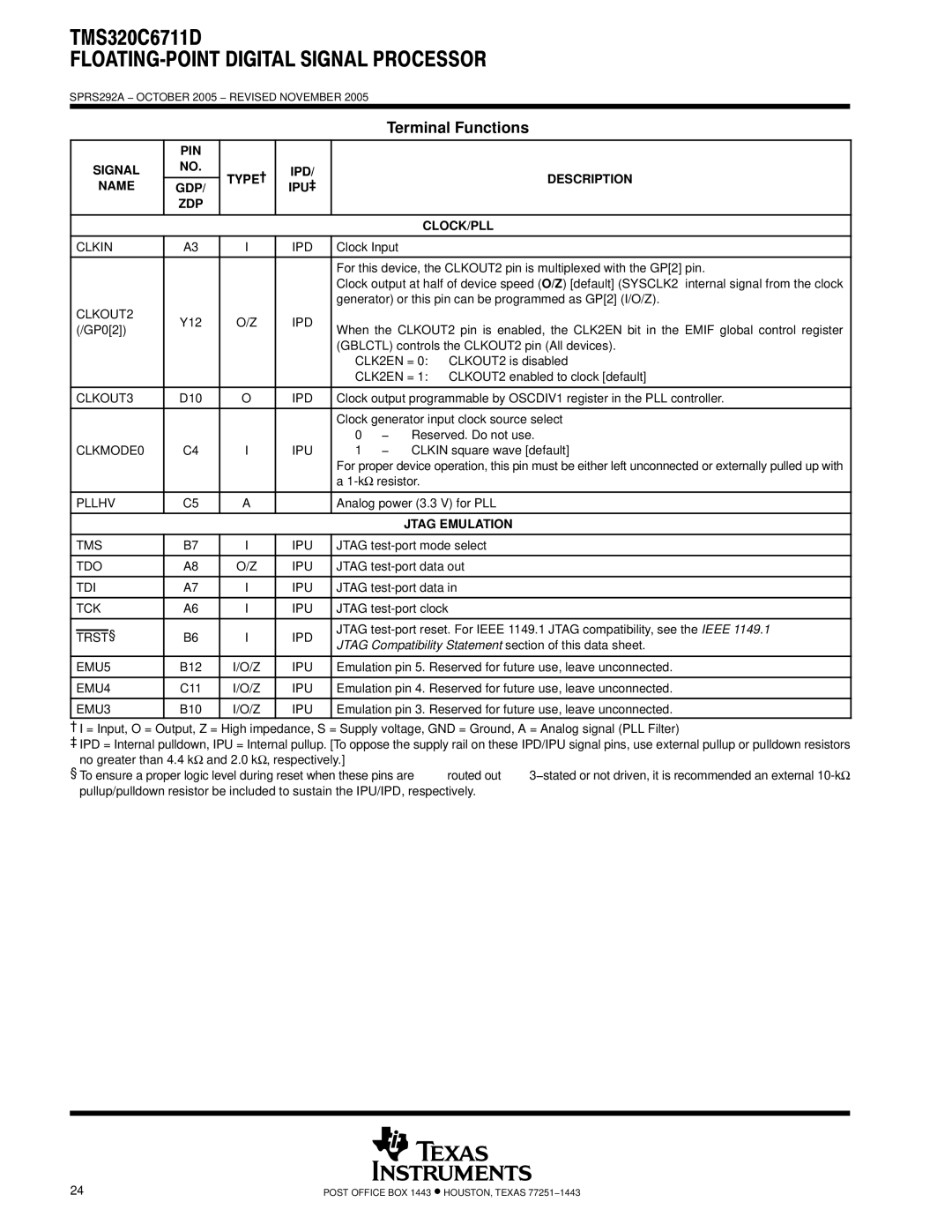

| Terminal Functions |

|

|

| PIN |

|

|

|

|

|

| SIGNAL | NO. | TYPE† | IPD/ |

|

| DESCRIPTION | |

|

|

|

| |||||

| NAME | GDP/ | IPU‡ |

|

| |||

|

|

|

|

| ||||

|

|

| ZDP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| CLOCK/PLL |

|

|

|

|

|

|

| ||

| CLKIN | A3 | I | IPD | Clock Input | |||

|

|

|

|

|

|

| ||

|

|

|

|

|

| For this device, the CLKOUT2 pin is multiplexed with the GP[2] pin. | ||

|

|

|

|

|

| Clock output at half of device speed (O/Z) [default] (SYSCLK2 internal signal from the clock | ||

|

|

|

|

|

| generator) or this pin can be programmed as GP[2] (I/O/Z). | ||

| CLKOUT2 | Y12 | O/Z | IPD |

|

|

| |

| (/GP0[2]) | When the CLKOUT2 pin is enabled, the CLK2EN bit in the EMIF global control register | ||||||

|

|

|

| |||||

|

|

|

|

|

| (GBLCTL) controls the CLKOUT2 pin (All devices). | ||

|

|

|

|

|

| CLK2EN = 0: CLKOUT2 is disabled | ||

|

|

|

|

|

| CLK2EN = 1: CLKOUT2 enabled to clock [default] | ||

|

|

|

|

|

|

| ||

| CLKOUT3 | D10 | O | IPD | Clock output programmable by OSCDIV1 register in the PLL controller. | |||

|

|

|

|

|

|

| ||

|

|

|

|

|

| Clock generator input clock source select | ||

|

|

|

|

|

| 0 | − | Reserved. Do not use. |

| CLKMODE0 | C4 | I | IPU | 1 | − | CLKIN square wave [default] | |

|

|

|

|

|

| For proper device operation, this pin must be either left unconnected or externally pulled up with | ||

|

|

|

|

|

| a | ||

|

|

|

|

|

|

| ||

| PLLHV | C5 | A |

| Analog power (3.3 V) for PLL | |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| JTAG EMULATION |

|

|

|

|

|

|

| ||

| TMS | B7 | I | IPU | JTAG | |||

|

|

|

|

|

|

| ||

| TDO | A8 | O/Z | IPU | JTAG | |||

|

|

|

|

|

|

| ||

| TDI | A7 | I | IPU | JTAG | |||

|

|

|

|

|

|

| ||

| TCK | A6 | I | IPU | JTAG | |||

|

|

|

|

|

|

| ||

|

|

|

|

|

| JTAG | ||

| TRST§ | B6 | I | IPD | ||||

| JTAG Compatibility Statement section of this data sheet. | |||||||

|

|

|

|

|

| |||

|

|

|

|

|

| |||

| EMU5 | B12 | I/O/Z | IPU | Emulation pin 5. Reserved for future use, leave unconnected. | |||

|

|

|

|

|

| |||

| EMU4 | C11 | I/O/Z | IPU | Emulation pin 4. Reserved for future use, leave unconnected. | |||

|

|

|

|

|

| |||

| EMU3 | B10 | I/O/Z | IPU | Emulation pin 3. Reserved for future use, leave unconnected. | |||

†I = Input, O = Output, Z = High impedance, S = Supply voltage, GND = Ground, A = Analog signal (PLL Filter)

‡IPD = Internal pulldown, IPU = Internal pullup. [To oppose the supply rail on these IPD/IPU signal pins, use external pullup or pulldown resistors no greater than 4.4 kΩ and 2.0 kΩ, respectively.]

§To ensure a proper logic level during reset when these pins are both routed out and 3−stated or not driven, it is recommended an external

24 | POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251−1443 |