SPRS292 − OCTOBER 2005

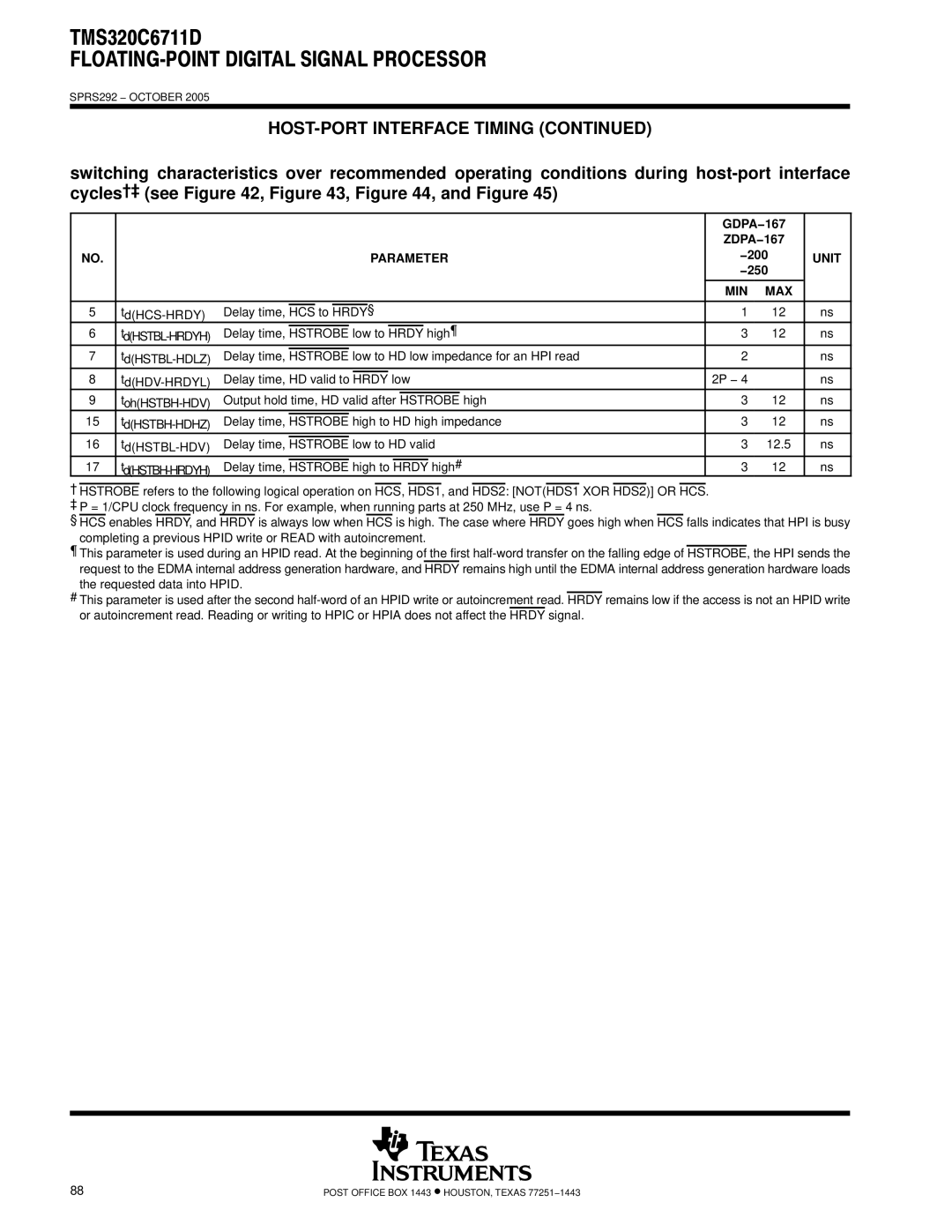

HOST-PORT INTERFACE TIMING (CONTINUED)

switching characteristics over recommended operating conditions during

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| GDPA−167 |

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ZDPA−167 |

| |

NO. |

|

|

|

|

|

|

|

| PARAMETER | −200 |

| UNIT | |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| −250 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| MIN | MAX |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5 | Delay time, |

| to |

|

|

|

| § |

|

|

|

|

|

|

| 1 | 12 | ns | |

HCS | HRDY | ||||||||||||||||||

6 | Delay time, |

|

|

|

| low to |

|

|

| high¶ | 3 | 12 | ns | ||||||

HSTROBE | HRDY | ||||||||||||||||||

7 | Delay time, |

|

|

|

| low to HD low impedance for an HPI read | 2 |

| ns | ||||||||||

HSTROBE |

| ||||||||||||||||||

8 | Delay time, HD valid to |

|

| low | 2P − 4 |

| ns | ||||||||||||

HRDY |

| ||||||||||||||||||

9 | Output hold time, HD valid after |

|

|

| high | 3 | 12 | ns | |||||||||||

HSTROBE | |||||||||||||||||||

15 | Delay time, |

|

|

| high to HD high impedance | 3 | 12 | ns | |||||||||||

HSTROBE | |||||||||||||||||||

16 | Delay time, |

|

|

|

| low to HD valid | 3 | 12.5 | ns | ||||||||||

HSTROBE | |||||||||||||||||||

17 | Delay time, |

|

|

|

| high to |

|

|

| high# | 3 | 12 | ns | ||||||

HSTROBE | HRDY | ||||||||||||||||||

†HSTROBE refers to the following logical operation on HCS, HDS1, and HDS2: [NOT(HDS1 XOR HDS2)] OR HCS.

‡P = 1/CPU clock frequency in ns. For example, when running parts at 250 MHz, use P = 4 ns.

§HCS enables HRDY, and HRDY is always low when HCS is high. The case where HRDY goes high when HCS falls indicates that HPI is busy completing a previous HPID write or READ with autoincrement.

¶ This parameter is used during an HPID read. At the beginning of the first

#This parameter is used after the second

88 | POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251−1443 |