Momentum

USE 101

Training

USE 101 10 Version

November

Document Set

Installing and using this product

Preface

Preface

Contents

Part Communication Ports 109 Using the Modbus Ports 111

Overview of Momentum Option Adapters

Assembling Momentum Components

Chapter Using the I/OBus Port 171

Chapter

141

181

Chapter Mapping an I/OBus Network with Modsoft 247

Configuring a Modbus Plus Network in Modsoft

Part Concept 307 Configuring an M1 CPU with Concept 309

257

Saving to Flash in Modsoft 303

Mapping an I/OBus Network with Concept 361

Saving to Flash with Concept 399

Appendix B

417

Saving to Flash 399

Contents Xiv

About This Book

Version Change

About Book

Related

You may find the following other manuals useful

Documentation

Getting Started

At a Glance

Purpose

This Part

Getting Started

Overview of Momentum M1 Processor Adapters

To local and distributed I/O

This chapter describes the M1 Processor Adapters

This Chapter This chapter contains the following sections

Characteristics of M1 Processor Adapters

Section Introducing the M1 Processor Adapters

Overview

Common communication bus

Front Panel illustration

Label Description

Overview of Ports

Introduction

Ports Per

Processor

OBus Port

Memory and Performance Characteristics

Internal Memory

Flash RAM

Clock Speed

Below

Processor 984LL Flash RAM

Program Memory

Input and Output

References

984LL Executive IEC Executive Registers Discretes

Power Supply

Supplied by

Base

Refer to 870 Use 002 00 V Momentum I/O Base User Guide

Section Features of Each Processor Adapter

Specifications for each Processor Adapter

Features, an illustration and specifications

CCS 700

Overview

Status Function

Input and Output References

Servicing

Specifications

Safety Parameters

Mechanical

Operating Conditions

Overview

LED

Specifications

CCS 760

984LL Input and Output References

IEC Input and Output References

Temperature 40 ... +85 degrees C Humidity 95% noncondensing

CCC 760

LED

Specifications

CCS 780

LED

Specifications

CCC 780

LED

Specifications

Features, a illustration and specifications

CCC 960

Indicato Status Pattern

RUN

Specifications

Scantime Formula for 984LL Exec Example

Processor Adapter, including key

CCC 960 30 will not operate in a

Label Description

Indicator Status Pattern

Specifications

Scantime Formula for 984LL Exec Example

CCC 980

LED

Specifications

Scantime Formula for 984LL Exec Example

Overview

Label Description

LED

Specifications

Scantime Formula for 984LL Exec Example

Overview of Momentum Option Adapters

This Chapter

This chapter contains the following sections

Basic Features of Option Adapters

Section Introducing the Momentum Option Adapters

Front panel components and specifications

Section Serial Option Adapter

This Section

This section includes the following topics

An LED indicator

Battery compartment

Modbus Port 2 connector

Front Panel Components

Green

Pinouts for

Modbus Port

Pin For RS232 For RS485

Specifications

Time-of-Day Clock

Specifications

Section Modbus Plus Option Adapter

This section contains the following topics

Address switches

Pin D-shell connector for Modbus Plus communications

Connector, and battery compartment

Pattern Meaning

Switches

Switches in this illustration are set to address

Modbus Plus

Address

Specifications

Specifications

Section Redundant Modbus Plus Option Adapter

Two 9-pin D-shell connectors for Modbus Plus communications

Three LED indicators

Compartment and Modbus Plus connectors

MB+ ACT

MB+ ACT Flash

Patterns

Status of the Modbus Plus node

Modbus Plus

Specifications

Option Adapters

Option Adapters

Assembling Momentum Components

How to disassemble them

Section Assembling a CPU

Assembling a Processor Adapter and I/O Base

Connections at three points

Procedure

Assembling a Base Processor Adapter and an I/O Base

Step

Procedure Assembling a Processor Adapter and an Base

Next Step

Personnel

Disassembling a Processor Adapter from an I/O Base

Processor Adapter from an I/O base

Step Action

Disassembling a Processor Adapter from an I/O Base

Section Assembling a CPU with an Option Adapter

Assembling a Processor Adapter and an Option Adapter

Assembling an Processor Option Adapter

PIN Alignment

Next Step

Mounting the Assembled Adapters on the I/O Base

Assembled Processor and Option Adapter on an I/O base

Front of the I/O base

Two slots on the sides of the I/O base

Procedure Mounting the Assembled Adapters on an I/O Base

Mounting the Assembled Adapters on the I/O Base

Disassembling a Module with an Option Adapter

Tools Required

Procedure Removing the Adapter Assembly from the I/O Base

Exposed Circuitry in Battery Compartment

103

Procedure Disassembling An Option Adapter and M1 Processor

Section Installing Batteries in an Option Adapter

Installation Guidelines

Time-of-day clock in the event that the CPU loses power

While handling the equipment during battery maintenance

Battery

Removing

Replacing Following illustration Batteries Monitor

For Concept

Section Labeling the CPU

Guidelines for Labeling the CPU

Fill-In Label

Example of a a fill-in label is illustrated below

Communication Ports

Processor Adapters and Option Adapters

Communication Ports 110

Using the Modbus Ports

Accessories and pinouts

Accessories, and provides pinouts

Section Modbus Port

Connector Type

Modbus Port

Baud

Parity

Mode/Data Bits

Stop Bit Modbus Address

Default

Feature

Parameters

Auto-Logout

Cable Accessories for Modbus Port

Cables

Electric

Length Part Number

Pinouts for Modbus Port

Pinout

118

Topics

Features of an

Two Types

Port

RS485 Port

Comm Protocol

Modbus network address

RS232 protocol

Four-Wire Cabling Schemes for Modbus RS485 Networks

Label Description Part Number

125

Two-Wire Cabling Schemes for Modbus RS485 Networks

Potential for Multimaster Conflicts

Cable

Require the special master communication cable

Multimaster

Slave Cabling

Two-Wire Cabling Schemes for Modbus RS485 Networks

Scheme. This cable is 10 long and has a blue boot

Cable for Modbus RS485 Networks

Network for Momentum components

Master

Boot

Interconnect

Other Premade

Custom Cable

Vendors

Crimping Tool

Connectors for Modbus RS485 Networks

RS485 network for Momentum components

Custom Cabling network

Terminating Devices for Modbus RS485 Networks

Terminating

Resistor Plugs

Shunt Plugs

Pinouts for Modbus RS485 Networks

Pin Function

Pin D-Shell

For RS485. The metal shell is connected to chassis ground

137

Connector T Base DB9 Base

Modbus RS485

Connector T Base RJ45 Base

Resistor Plugs Terminating RJ45 Resistor Plugs

Using the Ethernet Port

Section Ethernet Port

Ethernet Port

Network Design Considerations

Control Networks Must be Isolated from MIS Data Networks

Networks

Supervisory

Combined

Handling

Security

Cabling Schemes

On a central Ethernet hub

As shown in the following table

Pinouts

Components

Pin

Assigning Ethernet Address Parameters

150

151

Using Bootp Lite to Assign Address Parameters

Refer to the Bootp Lite user documentation for instructions

Specifying Addresses Stopping Processor

Reading Ethernet Network Statistics

By the user

Statistics

Follows

Description

Framing Errors

Overflow Errors

CRC Errors

Words 16, 17 High Word Not used, always

Errors

Words 26

Transmit Buffer

157

Section Establishing a Connection with an Ethernet Module

What’s in this

Section

Using the Network Options Ethernet Tester

Establishing a Connection with an Ethernet Module

160

161

Section Accessing Embedded Web Pages

Accessing the Web Utility Home

Section CCC 960 30 and 171 CCC 980 30 Web Pages

Momentum M1E Web Pages

Link Results

Configuration

Its status. It has the following links

Links and LED indicators

M1E I/O Status

Transmit Statistics Receive Statistics Functioning Errors

Ethernet

Following links

Contacting Schneider Automation

Technical Assistance

Momentum M1E Indicators

Indicators

Adapter LED

Table below

Using the I/OBus Port

This chapter contains the following topics

Bus Port

As many as 255 slave devices over an Interbus cable

How I/OBus Works

Network Status Indication in the M1 Ethernet Module

Guidelines for I/OBus Networks

Distance

Between Nodes Number

176

Cable Accessories

Low Profile

178

Pin Wire Color

Pin Wire Color Ingoing Connection

Using the I/OBus Port 180

Using the Modbus Plus Ports

Modbus Plus ports are available with

172 PNN 210 Option Adapter Single Port PNN 260

Modbus Plus Features for Momentum

Introduction Cluster Mode Nodes

Two Types of Modbus Plus Networks

184

Standard Cabling Schemes

Between Nodes

Momentum

Network

Used

Cluster Mode Cabling Schemes

Clusters in a

Minimum length of cable between clusters is 10 ft m

Cluster Scheme

Second cluster

Cable Accessories for Modbus Plus Networks

Cable Within

Clusters

192

Modbus Plus Connector T XTS 020 DB9 base

Pinouts and Wiring Illustrations for Modbus Plus Networks

Plus network for Momentum components

195

Modbus Plus Connector T DB9 Base

RJ45 Shielded Connector

DB9 Connector

197

Modbus Plus Addresses

Will be passed from device to device

Sequence

Node Address X10 Setting X1 Setting

Peer Cop

Effect of Using

How Peer Cop

Data Is Sent

Received

Using the Modbus Plus Ports 202

To Flash using Modsoft

Modsoft

For Information On

Page

Configuring an M1 CPU with Modsoft

Chapter contains the following topics

Section Configuring the Processor Adapter

Modsoft

Starting from the Configuration Overview editor

Selecting an M1 Processor Adapter

Follow the steps below to select an M1 Processor Adapter

208

Configuration

Specifying an M1 Processor Type

Which Type

Should Choose?

Push Enter

Default Configuration Parameters

12.0K Adapter Parameters

Defaults for an

Adapter Parameters

Default Values Here are the default parameters

Parameter 4K Adapter 12.0K Adapter 18.0K Adapter

Changing the Range of Discrete and Register References

Step Action

Fields in the Configuration Overview screen

Words allocated the configuration extension memory

Changing the Size of Your Application Logic Space

Changing the Number of Segments

For I/OBus

For All Other

Cases

Type the new number of segments

Changing the Size of the I/O Map

Your Processor Adapter supports an I/OBus network

All Other

Processors

I/O Map

Establishing Configuration Extension Memory

Configuration extension memory

Pull-down list

How Much

Section Configuring Option Adapter Features

Clock features of the Momentum Option Adapters

Reserving and Monitoring a Battery Coil

Configuration Overview editor in Modsoft

Battery Coil

Reserving a

225

Setting up the Time-of-Day Clock

Block of eight 4 x registers

Reserving

Registers for TOD Clock

Next Step Setting the time

Reserving Registers for the TOD Clock

Setting the Time

Option

Running while you are setting the bits

Setting

Status Bits

Bits

Clock

Describe how to interpret the time-of-day clock registers

Reading the Time-of-Day Clock

Reading

Clock Example

Section Modifying Communication Port Parameters

Parameters

Accessing the Port Editor Screen

Screen is accessed from the Configuration Overview editor

How To Get

Values shown for Port

Parameters Which Should Not Be Changed

Stop Bit

Head-Slot

Changing the Mode and Data Bits

If the mode is RTU, the number of data bits is always

If the mode is ASCII, the number of data bits is always

Possible modes RTU or Ascii

Step

Checking. The factory-set default is Even parity

Changing Parity

Changing the Baud Rate

Default for both ports is address

Changing the Modbus Address

Modbus networks

Changing the Delay

Delay Timing

Valid Delay

Values

Changing the Protocol on Modbus Port

Protocol on Modbus Port

Accessing and Editing the I/O Map

Section Mapping the Local I/O Points

Base are the local I/O for that processor

Local base unit

Map

Editing the Local I/O Map

Assign the appropriate state RAM references to the unit

Bus a

Special Case

Configuring an M1 CPU with Modsoft 246

Mapping an I/OBus Network with Modsoft

Topics

Settings

Parameter Setting

Supporting an I/O Map for an I/OBus Network

Screen

249

Accessing an I/O Map Screen for an I/OBus Network

Next Step Editing the I/OBus I/O Map

Editing the I/OBus I/O Map

Processor Adapter Max. Modules Max. I/O Bits

Move the cursor onto the desired model number and push Enter

254

Codes

Its I/O type but not its specific model or name

Screens to define the parameters for these InterBus modules

Identifier Code Type

Generic InterBus Module Identifier

Codes

Pages

Configuring a Modbus Plus Network in Modsoft with Peer Cop

For This Topic

Describes the default screen

Section Getting Started

Accessing the Peer Cop Configuration Extension Screen

Reserve

Default Peer Cop Screen

Description

Networks

Section Using Modbus Plus to Handle I/O

Devices on the Network

Strategy used to assign addresses

Momentum module on the network

Strategy

Defining the Link and Accessing a Node

Link and access a node

Popup menu

Next Step Confirming the Peer Cop summary information

Step Action Push Enter

Timeout

On Error

Confirming the Peer Cop Summary Information

269

270

Next Step Specifying references for input data

Specifying References for Input Data

Device

Requirements

Is required to handle this module

273

274

Next Step Accessing the remaining devices

Accessing the Remaining Devices

Address 3, using the AddNode command

277

Completing the I/O Device Configuration in Peer Cop

Register

Assignments

Completed

Screen Node Completed

Completed Peer Cop screen for node 3 should look like this

Completed Peer Cop screen for node 4 should look like this

Completed Peer Cop screen for node 5 should look like this

Section Passing Supervisory Data over Modbus Plus

Supervising device

MB+ Address

Configuring a Node to Exchange Data

284

285

For our example, we will use the default setting

As an increment of 20 ms

Specifying References for Input and Output Data

Address 2. This device will

Modbus Plus address

Supervisor

Defining the Specific Output

Defining

Global Inputs

Specify the global input references

Defining the Global Inputs

Next Step Defining the references for the next node

Defining the References for the Next Node

Link and Node

Defining Specific

Outputs

Defining Specific Outputs

294

Defining Global

Inputs

Next Step Defining references for the supervisory computer

Defining References for the Supervisory Computer

Handle the M1 CPUs at addresses 2

Specific inputs

Will be received by both of the M1 CPUs

298

Specifying References for Node

300

Accesses node 3 and defines the references for that node

Completing the Configuration

Node A Node setting Specifying

References for that CPU

Flash using Modsoft

Saving to Flash in Modsoft

Application logic and state RAM values will be preserved

This Chapter This chapter contains the following topics

Preparing to Save to Flash

Saving to Flash

Saving to Flash

Save-to-Flash Procedure

To Flash using Concept

Concept

Page

Configuring an M1 CPU with Concept

This chapter explains how to configure a CPU using Concept

Concept

Using Concept

PLC

312

313

Step Action Choose your PLC type from the CPU/Executive menu

Defaults for a 2.4K Machine

Defaults for a 12.2K Machine

Defaults for an 18.4K Machine

Parameter 4K Machine 12.2K Machine 18.4K Machine

Maximum of state memory displayed at the top of the dialog

319

Configuration screen

Changing the Size of the Full Logic Area

Cop

Understanding the Number of Segments

Only the First

Segment is

Solved

Area

Processors for

OBus Networks

Devices on the network bus

From the Configure menu, select I/O Map

Establishing Configuration Extension Memory for Peer Cop

Adjust the amount of Configuration Extension memory

Step Action From the Configure menu, select Peer Cop

Result The Peer Cop dialog box appears

Clock features of the Momentum Option Adapters using Concept

Service release

Reserve a battery coil

Dialog box in Concept

Reserving a Battery Coil

Step Action Click the check box next to Battery Coil

Battery Coil When the battery is low

Monitoring

Setting up the Time-of-Day Clock

332

333

Time bits. The CPU must be running

Registers

Default parameters

Section Modifying Modbus Port Parameters

Accessing the Modbus Port Settings Dialog Box

How to Get There

Default Settings

Changing the Baud Rate

Changing Mode and Data Bits

One of two possible modes RTU or Ascii

Parity checking. The factory-set default is Even parity

Stop Bit Should Not Be Changed Changing Parity

Follow the steps in the table below to change the delay

Ms increments

Set the Stop Bit at Bridge mode is not supported

To change the Modbus Address

Step Address

To change the Protocol on Modbus Port

Overview

Accessing the Ethernet / I/O Scanner Screen

Ethernet / I/O Scanner dialog box in Concept

346

Ethernet Configuration Options

Use Bootp

Specify IP

Setting Ethernet Address Parameters

IP Address

Gateway

349

Configuring I/O

Parameters for I/O scanning

Unit ID Health Timeout Rep Rate

On the down arrow and selecting it, as shown

Read

First address to read to

Write

First address to write to

Description column

Completing the I/O Configuration

Copy, Cut, Paste, Delete, Sort and Fill Down buttons

Cut and Paste

Delete

Sort

Fill Down

Down button, following the steps in the table below

Map Screen From the Configure menu

Result The I/O Map dialog box appears

Map Local I/O Map

Module Selection

Editing the Local Map

Configuring an M1 CPU with Concept 360

Mapping an I/OBus Network with Concept

Reserved Words

Segments

From the Configure menu, select I/OMap

Result The Remote I/O Bus Drop dialog appears

Network depends on your Processor Adapter and its executive

Perform the steps in the following table

Processor Adapter Executive Max. Modules Max. I/O Bits

366

367

Mapping an I/OBus Network with Concept 368

Configuring a Modbus Plus Network in Concept with Peer Cop

Configuring a Modbus Plus Network in Concept with Peer Cop

Accessing the Peer Cop Dialog Box

Accessing the Screen

Adjusting the Amount of Extension Memory

Memory Size Words

Other Default Settings in the Peer Cop Dialog Box

Modbus Plus communications have been restored

Last Value

Option Effect

Section Using Modbus Plus to Handle I/O

Devices on the Network

Default Last Value setting to Hold on timeout

Changing the Peer Cop Summary Information

379

ADI 340 00 16-point input module

Required to handle this module

381

382

Next Step Specifying output references

Specifying References for Output Data

170 AD0 340 00 16-point output module

Specific output reference with a length of one word 16 bits

385

Specifying References for Output Data

Section Passing Supervisory Data over Modbus Plus

Devices on the Network

Ms and Last Value Clear on timeout

Address 2 to

Outputs broadcast by the supervisory controller

Peer Cop dialog box

390

Input reference

392

Defining the References for the Next Node

394

Supervisory PLC at Modbus Plus address

Defining References for the Supervisory PLC

Peer Cop screens to handle the M1 CPUs at addresses 2

Specific Inputs

Global Outputs

Received by each of the M1 CPUs

USE 101 10

Saving to Flash with Concept

Saving to Flash with Concept

Result The Online Control Panel appears

Saving to Flash

Appendices

For Information On See Appendix

Page

Ladder Logic Elements Instructions

This Appendix

This appendix contains the following topics

Symbols

Symbol Meaning Nodes Consumed

Standard Ladder Logic Elements

Ladder Logic

Symbol Meaning

Counter and Timer Instructions

Logic Instructions

Integer Math Instructions

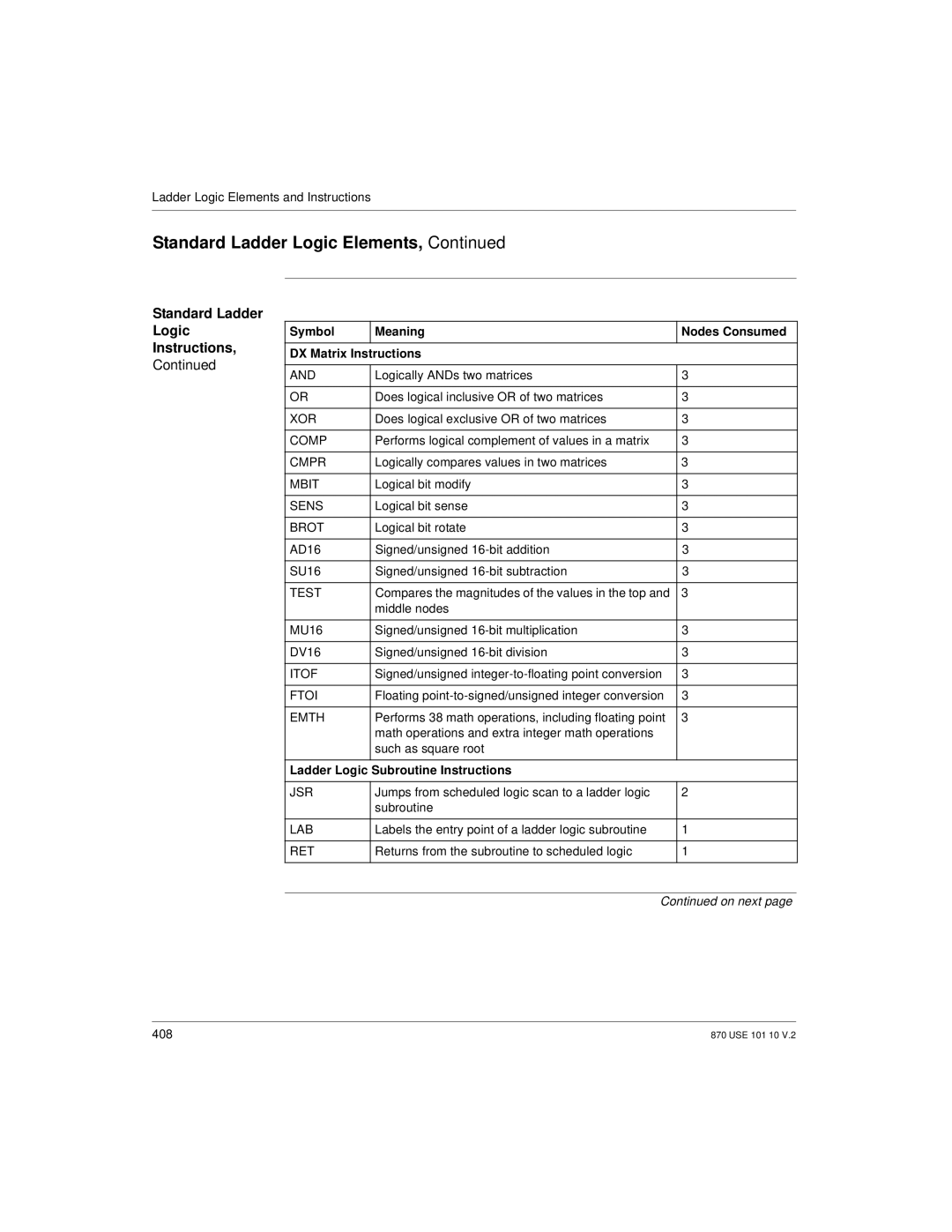

Symbol Meaning Nodes Consumed DX Matrix Instructions

Standard Ladder Logic Instructions

Ladder Logic Subroutine Instructions

Standard Ladder Logic

Other Special Purpose Instructions

DX Loadable Support

Diagram of Stat

Special Stat Instruction

Avoid Discretes

Specify Length

Content

Top Node

Bottom Node

Word Description

Word

415

This Word Indicates the Status of These I/O Modules 112

128

Run LED Flash Patterns and Error Codes

Number of Blinks Code hex Error

Run LED Flash Pattern and Error

419

Run LED Flash Patterns and Error Codes 420

Index Numerics

Address strategy, 264, 282, 377, 388 two types, 257

423

Index 424

North Andover, MA Seligenstadt