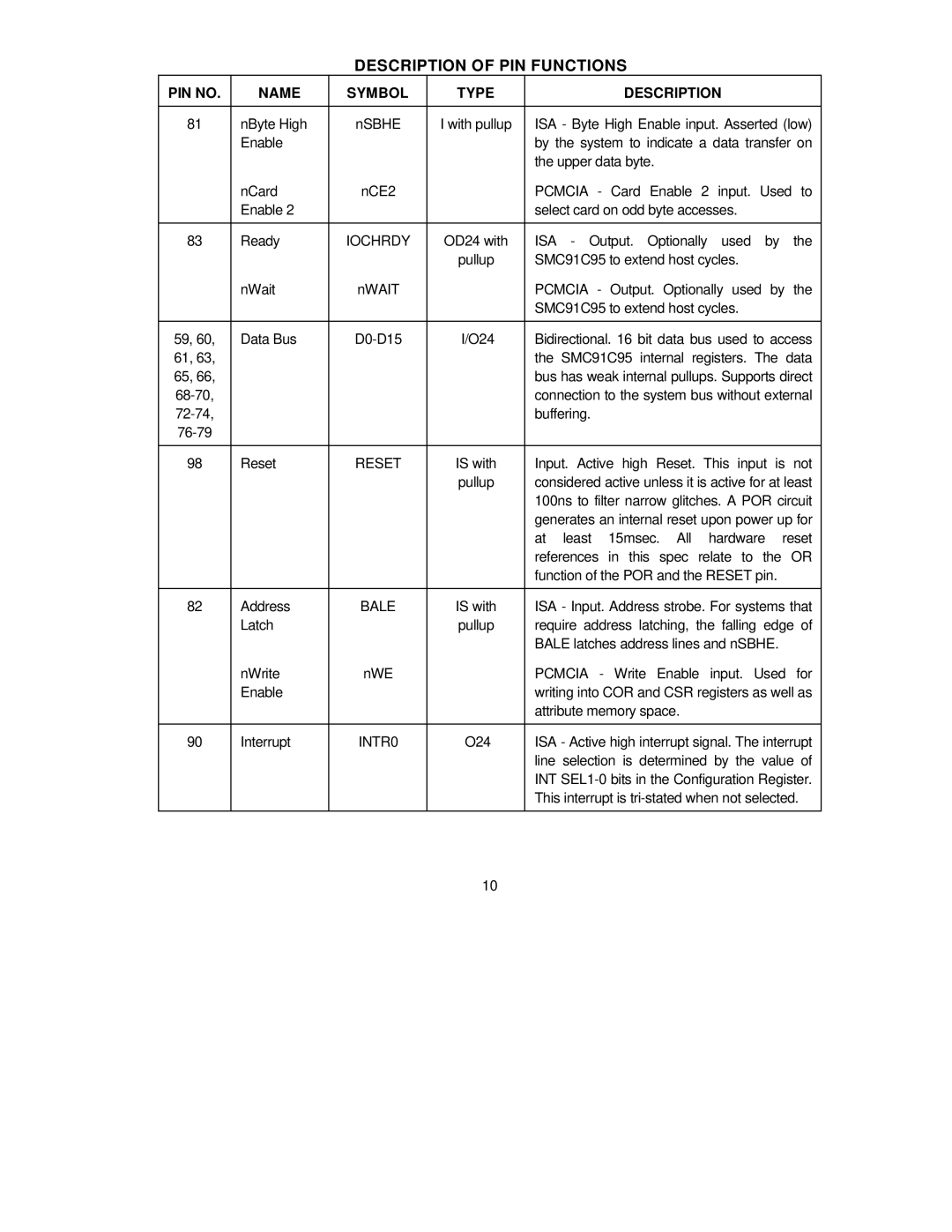

DESCRIPTION OF PIN FUNCTIONS

PIN NO. | NAME | SYMBOL | TYPE | DESCRIPTION |

|

|

|

|

|

81 | nByte High | nSBHE | I with pullup | ISA - Byte High Enable input. Asserted (low) |

| Enable |

|

| by the system to indicate a data transfer on |

|

|

|

| the upper data byte. |

| nCard | nCE2 |

| PCMCIA - Card Enable 2 input. Used to |

| Enable 2 |

|

| select card on odd byte accesses. |

|

|

|

|

|

83 | Ready | IOCHRDY | OD24 with | ISA - Output. Optionally used by the |

|

|

| pullup | SMC91C95 to extend host cycles. |

| nWait | nWAIT |

| PCMCIA - Output. Optionally used by the |

|

|

|

| SMC91C95 to extend host cycles. |

|

|

|

|

|

59, 60, | Data Bus | I/O24 | Bidirectional. 16 bit data bus used to access | |

61, 63, |

|

|

| the SMC91C95 internal registers. The data |

65, 66, |

|

|

| bus has weak internal pullups. Supports direct |

|

|

| connection to the system bus without external | |

|

|

| buffering. | |

|

|

|

| |

|

|

|

|

|

98 | Reset | RESET | IS with | Input. Active high Reset. This input is not |

|

|

| pullup | considered active unless it is active for at least |

|

|

|

| 100ns to filter narrow glitches. A POR circuit |

|

|

|

| generates an internal reset upon power up for |

|

|

|

| at least 15msec. All hardware reset |

|

|

|

| references in this spec relate to the OR |

|

|

|

| function of the POR and the RESET pin. |

|

|

|

|

|

82 | Address | BALE | IS with | ISA - Input. Address strobe. For systems that |

| Latch |

| pullup | require address latching, the falling edge of |

|

|

|

| BALE latches address lines and nSBHE. |

| nWrite | nWE |

| PCMCIA - Write Enable input. Used for |

| Enable |

|

| writing into COR and CSR registers as well as |

|

|

|

| attribute memory space. |

|

|

|

|

|

90 | Interrupt | INTR0 | O24 | ISA - Active high interrupt signal. The interrupt |

|

|

|

| line selection is determined by the value of |

|

|

|

| INT |

|

|

|

| This interrupt is |

|

|

|

|

|

10