I/O SPACE - BANK1 |

|

|

|

|

|

|

|

| ||

OFFSET |

|

| NAME |

| TYPE | SYMBOL | ||||

C |

| CONTROL REGISTER | READ/WRITE | CTR | ||||||

|

|

|

|

|

|

|

|

|

|

|

HIGH |

| 0 | RCV_ |

| PWRDWN | WAKEU | AUTO |

|

| 1 |

BYTE |

|

| BAD |

|

| P_EN | RELEASE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 0 | 0 | 0 | 0 | 0 | X | X | 1 | |

LOW |

| LE | CR |

| TE |

|

| EEPROM | RELOAD | STORE |

BYTE |

| ENABLE | ENABLE |

| ENABLE |

|

| SELECT |

|

|

|

| 0 | 0 | 0 | X | X | 0 | 0 | 0 | |

|

|

|

|

|

|

|

|

|

|

|

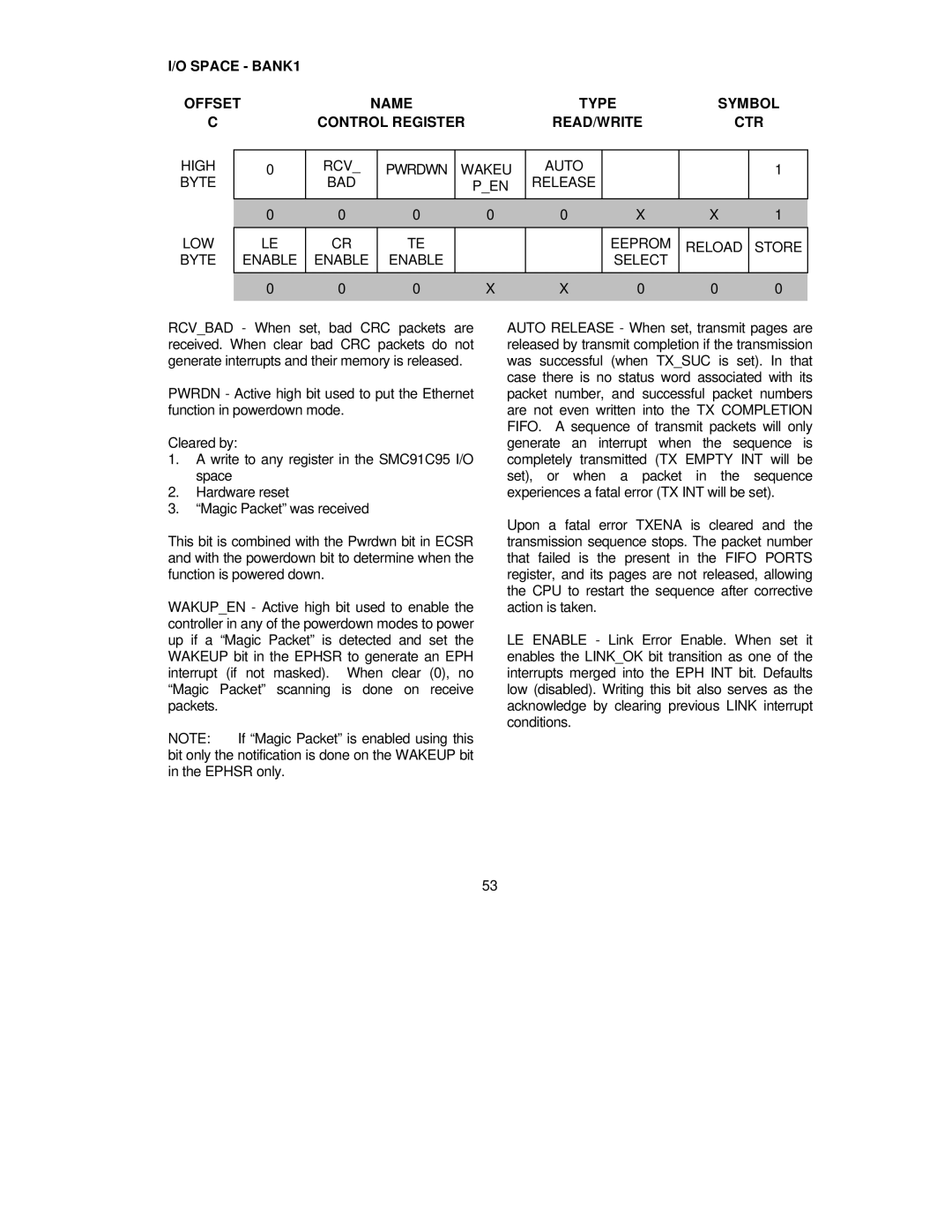

RCV_BAD - When set, bad CRC packets are received. When clear bad CRC packets do not generate interrupts and their memory is released.

PWRDN - Active high bit used to put the Ethernet function in powerdown mode.

Cleared by:

1.A write to any register in the SMC91C95 I/O space

2.Hardware reset

3.“Magic Packet” was received

This bit is combined with the Pwrdwn bit in ECSR and with the powerdown bit to determine when the function is powered down.

WAKUP_EN - Active high bit used to enable the controller in any of the powerdown modes to power up if a “Magic Packet” is detected and set the WAKEUP bit in the EPHSR to generate an EPH interrupt (if not masked). When clear (0), no “Magic Packet” scanning is done on receive packets.

NOTE: If “Magic Packet” is enabled using this bit only the notification is done on the WAKEUP bit in the EPHSR only.

AUTO RELEASE - When set, transmit pages are released by transmit completion if the transmission was successful (when TX_SUC is set). In that case there is no status word associated with its packet number, and successful packet numbers are not even written into the TX COMPLETION FIFO. A sequence of transmit packets will only generate an interrupt when the sequence is completely transmitted (TX EMPTY INT will be set), or when a packet in the sequence experiences a fatal error (TX INT will be set).

Upon a fatal error TXENA is cleared and the transmission sequence stops. The packet number that failed is the present in the FIFO PORTS register, and its pages are not released, allowing the CPU to restart the sequence after corrective action is taken.

LE ENABLE - Link Error Enable. When set it enables the LINK_OK bit transition as one of the interrupts merged into the EPH INT bit. Defaults low (disabled). Writing this bit also serves as the acknowledge by clearing previous LINK interrupt conditions.

53