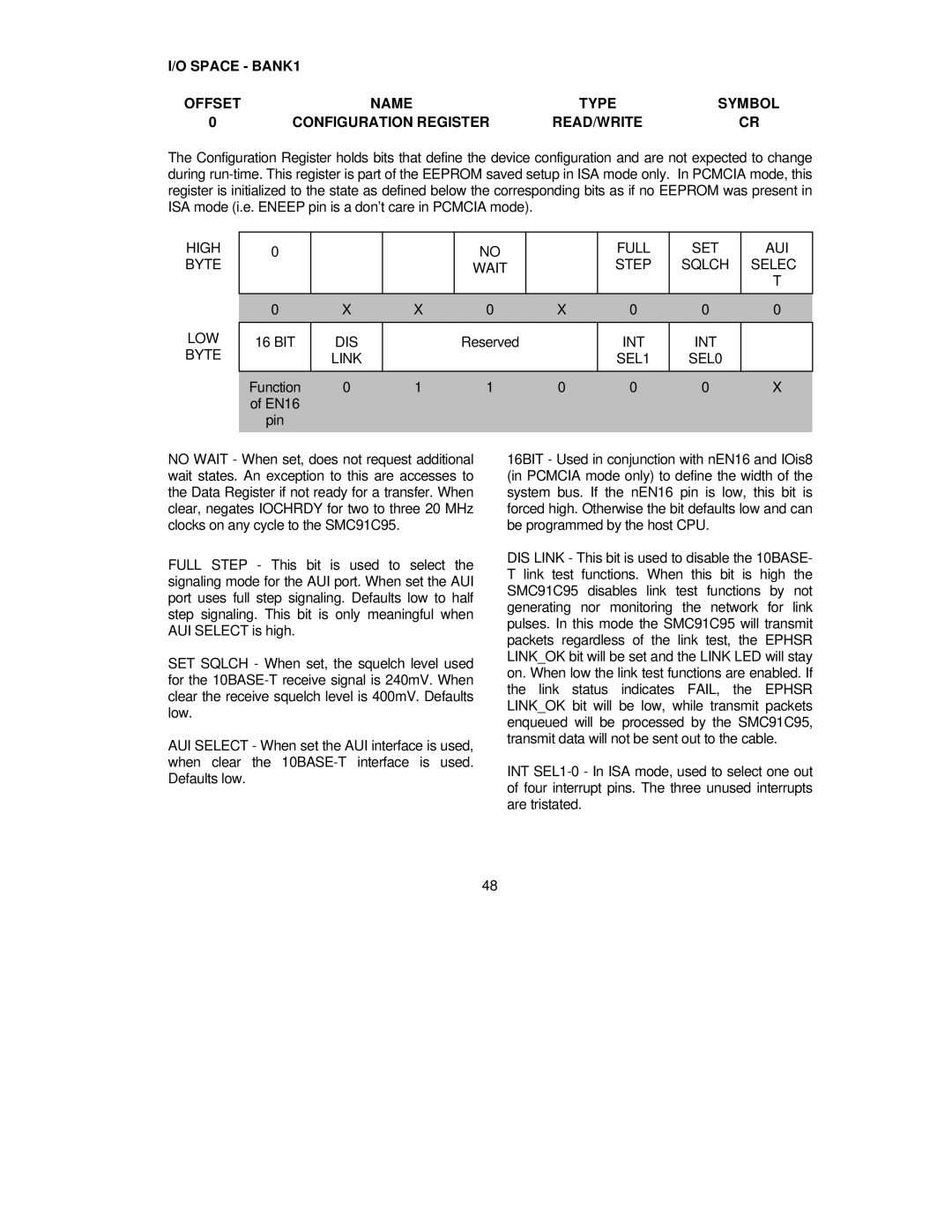

I/O SPACE - BANK1 |

|

| |

OFFSET | NAME | TYPE | SYMBOL |

0 | CONFIGURATION REGISTER | READ/WRITE | CR |

The Configuration Register holds bits that define the device configuration and are not expected to change during

HIGH | 0 |

|

| NO |

| FULL | SET | AUI |

BYTE |

|

|

| WAIT |

| STEP | SQLCH | SELEC |

|

|

|

|

|

|

|

| T |

| 0 | X | X | 0 | X | 0 | 0 | 0 |

LOW | 16 BIT | DIS |

| Reserved |

| INT | INT |

|

BYTE |

| LINK |

|

|

| SEL1 | SEL0 |

|

|

|

|

|

|

|

|

|

|

| Function | 0 | 1 | 1 | 0 | 0 | 0 | X |

| of EN16 |

|

|

|

|

|

|

|

| pin |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NO WAIT - When set, does not request additional wait states. An exception to this are accesses to the Data Register if not ready for a transfer. When clear, negates IOCHRDY for two to three 20 MHz clocks on any cycle to the SMC91C95.

FULL STEP - This bit is used to select the signaling mode for the AUI port. When set the AUI port uses full step signaling. Defaults low to half step signaling. This bit is only meaningful when AUI SELECT is high.

SET SQLCH - When set, the squelch level used for the

AUI SELECT - When set the AUI interface is used, when clear the

16BIT - Used in conjunction with nEN16 and IOis8 (in PCMCIA mode only) to define the width of the system bus. If the nEN16 pin is low, this bit is forced high. Otherwise the bit defaults low and can be programmed by the host CPU.

DIS LINK - This bit is used to disable the 10BASE- T link test functions. When this bit is high the SMC91C95 disables link test functions by not generating nor monitoring the network for link pulses. In this mode the SMC91C95 will transmit packets regardless of the link test, the EPHSR LINK_OK bit will be set and the LINK LED will stay on. When low the link test functions are enabled. If the link status indicates FAIL, the EPHSR LINK_OK bit will be low, while transmit packets enqueued will be processed by the SMC91C95, transmit data will not be sent out to the cable.

INT

48