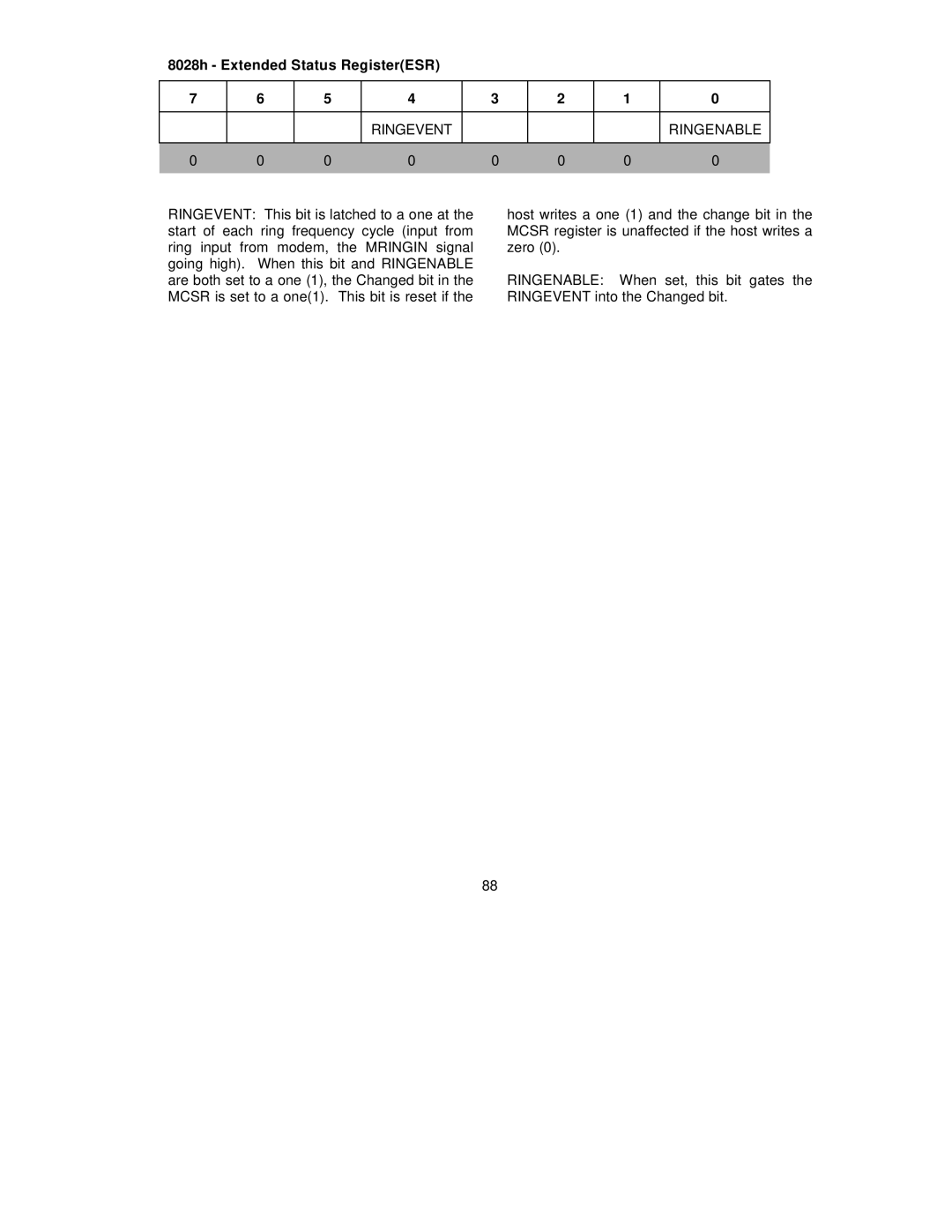

8028h - Extended Status Register(ESR)

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|

|

|

|

|

|

|

|

|

|

| RINGEVENT |

|

|

| RINGENABLE |

|

|

|

|

|

|

|

|

0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|

|

|

|

|

|

|

|

RINGEVENT: This bit is latched to a one at the start of each ring frequency cycle (input from ring input from modem, the MRINGIN signal going high). When this bit and RINGENABLE are both set to a one (1), the Changed bit in the MCSR is set to a one(1). This bit is reset if the

host writes a one (1) and the change bit in the MCSR register is unaffected if the host writes a zero (0).

RINGENABLE: When set, this bit gates the RINGEVENT into the Changed bit.

88