I/O SPACE - BANK0 |

|

|

|

OFFSET | NAME | TYPE | SYMBOL |

0 | TRANSMIT CONTROL | READ/WRITE | TCR |

| REGISTER |

|

|

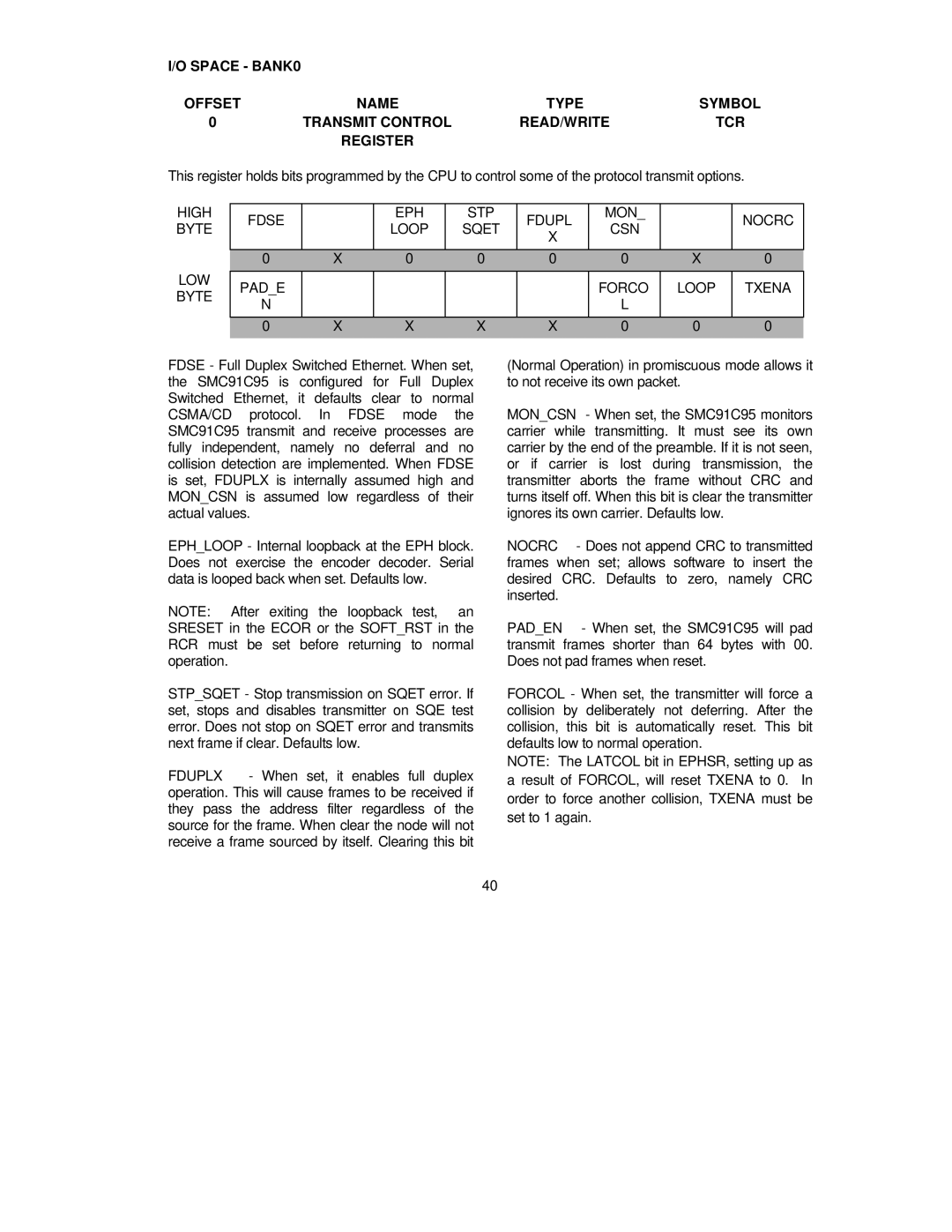

This register holds bits programmed by the CPU to control some of the protocol transmit options.

HIGH | FDSE |

| EPH | STP | FDUPL | MON_ |

| NOCRC |

BYTE |

| LOOP | SQET | CSN |

| |||

|

| X |

|

| ||||

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

| 0 | X | 0 | 0 | 0 | 0 | X | 0 |

LOW | PAD_E |

|

|

|

| FORCO | LOOP | TXENA |

BYTE |

|

|

|

| ||||

N |

|

|

|

| L |

|

| |

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

| 0 | X | X | X | X | 0 | 0 | 0 |

|

|

|

|

|

|

|

|

|

FDSE - Full Duplex Switched Ethernet. When set, the SMC91C95 is configured for Full Duplex Switched Ethernet, it defaults clear to normal CSMA/CD protocol. In FDSE mode the SMC91C95 transmit and receive processes are fully independent, namely no deferral and no collision detection are implemented. When FDSE is set, FDUPLX is internally assumed high and MON_CSN is assumed low regardless of their actual values.

EPH_LOOP - Internal loopback at the EPH block. Does not exercise the encoder decoder. Serial data is looped back when set. Defaults low.

NOTE: After exiting the loopback test, an SRESET in the ECOR or the SOFT_RST in the RCR must be set before returning to normal operation.

STP_SQET - Stop transmission on SQET error. If set, stops and disables transmitter on SQE test error. Does not stop on SQET error and transmits next frame if clear. Defaults low.

FDUPLX - When set, it enables full duplex operation. This will cause frames to be received if they pass the address filter regardless of the source for the frame. When clear the node will not receive a frame sourced by itself. Clearing this bit

(Normal Operation) in promiscuous mode allows it to not receive its own packet.

MON_CSN - When set, the SMC91C95 monitors carrier while transmitting. It must see its own carrier by the end of the preamble. If it is not seen, or if carrier is lost during transmission, the transmitter aborts the frame without CRC and turns itself off. When this bit is clear the transmitter ignores its own carrier. Defaults low.

NOCRC - Does not append CRC to transmitted frames when set; allows software to insert the desired CRC. Defaults to zero, namely CRC inserted.

PAD_EN - When set, the SMC91C95 will pad transmit frames shorter than 64 bytes with 00. Does not pad frames when reset.

FORCOL - When set, the transmitter will force a collision by deliberately not deferring. After the collision, this bit is automatically reset. This bit defaults low to normal operation.

NOTE: The LATCOL bit in EPHSR, setting up as a result of FORCOL, will reset TXENA to 0. In order to force another collision, TXENA must be set to 1 again.

40