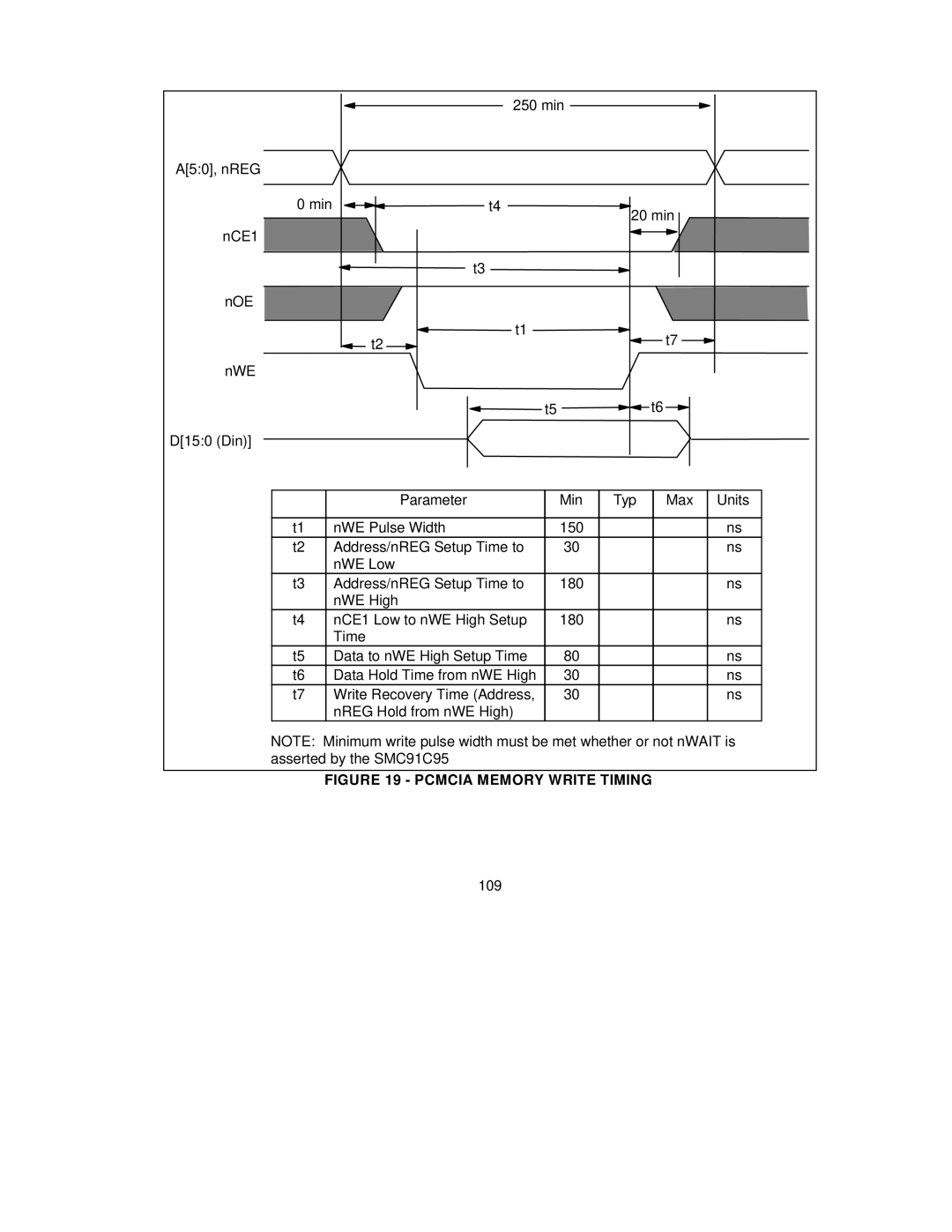

250 min

A[5:0], nREG

0 min ![]()

![]() t4

t4 ![]()

20 min

nCE1

t3 ![]()

nOE

![]() t1

t1 ![]()

t2 | t7 |

nWE

![]() t5

t5 ![]()

![]() t6

t6 ![]()

D[15:0 (Din)]

| Parameter | Min | Typ | Max | Units |

|

|

|

|

|

|

t1 | nWE Pulse Width | 150 |

|

| ns |

t2 | Address/nREG Setup Time to | 30 |

|

| ns |

| nWE Low |

|

|

|

|

t3 | Address/nREG Setup Time to | 180 |

|

| ns |

| nWE High |

|

|

|

|

t4 | nCE1 Low to nWE High Setup | 180 |

|

| ns |

| Time |

|

|

|

|

t5 | Data to nWE High Setup Time | 80 |

|

| ns |

t6 | Data Hold Time from nWE High | 30 |

|

| ns |

t7 | Write Recovery Time (Address, | 30 |

|

| ns |

| nREG Hold from nWE High) |

|

|

|

|

NOTE: Minimum write pulse width must be met whether or not nWAIT is

asserted by the SMC91C95