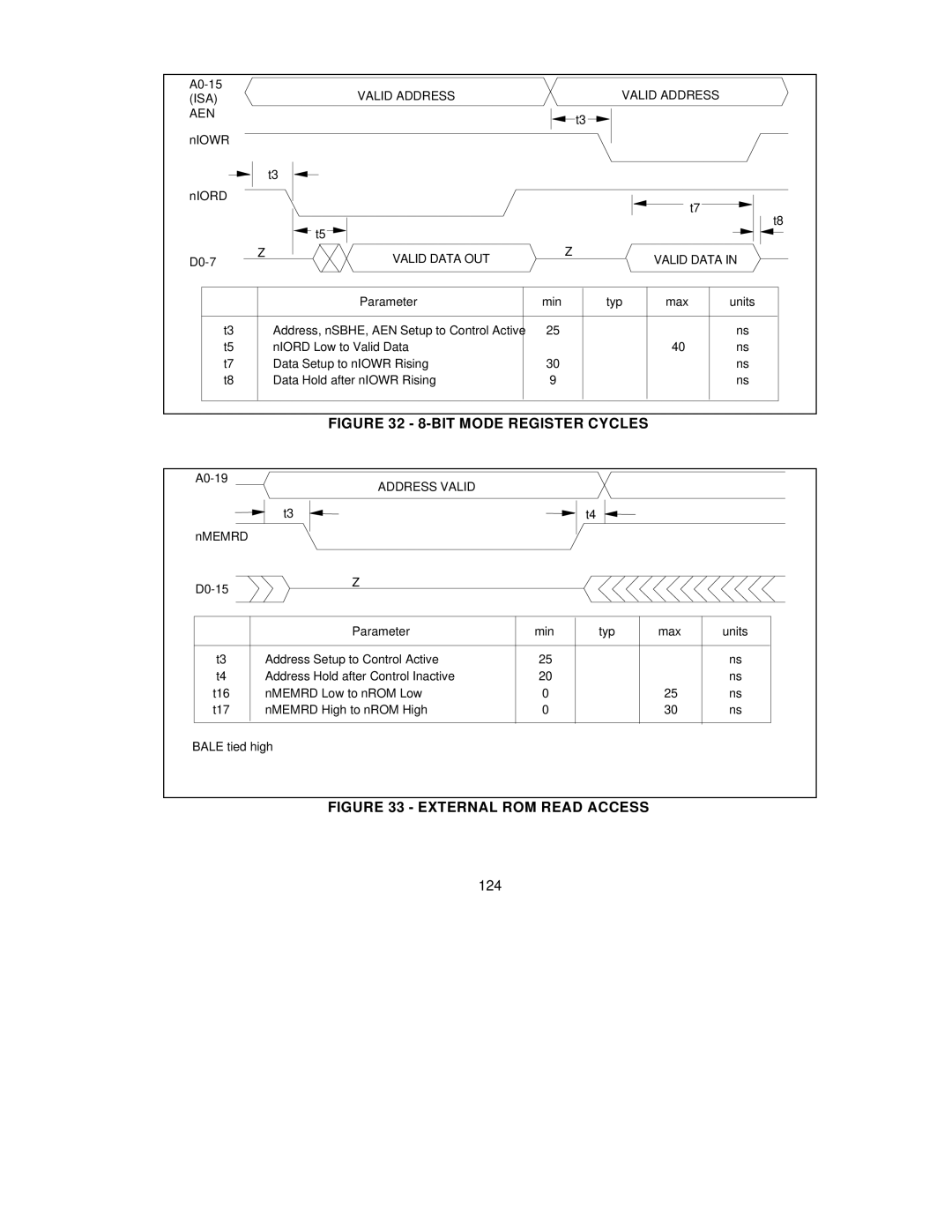

AEN

nIOWR

t3

nIORD

Z

VALID ADDRESS

t5

VALID DATA OUT

VALID ADDRESS

t3

t7

Z

VALID DATA IN

t8

| Parameter | min | typ | max | units |

|

|

|

|

|

|

t3 | Address, nSBHE, AEN Setup to Control Active | 25 |

|

| ns |

t5 | nIORD Low to Valid Data |

|

| 40 | ns |

t7 | Data Setup to nIOWR Rising | 30 |

|

| ns |

t8 | Data Hold after nIOWR Rising | 9 |

|

| ns |

|

|

|

|

|

|

FIGURE 32 - 8-BIT MODE REGISTER CYCLES

ADDRESS VALID

t3

t4

nMEMRD

Z

| Parameter | min | typ | max | units |

|

|

|

|

|

|

t3 | Address Setup to Control Active | 25 |

|

| ns |

t4 | Address Hold after Control Inactive | 20 |

|

| ns |

t16 | nMEMRD Low to nROM Low | 0 |

| 25 | ns |

t17 | nMEMRD High to nROM High | 0 |

| 30 | ns |

|

|

|

|

|

|

BALE tied high