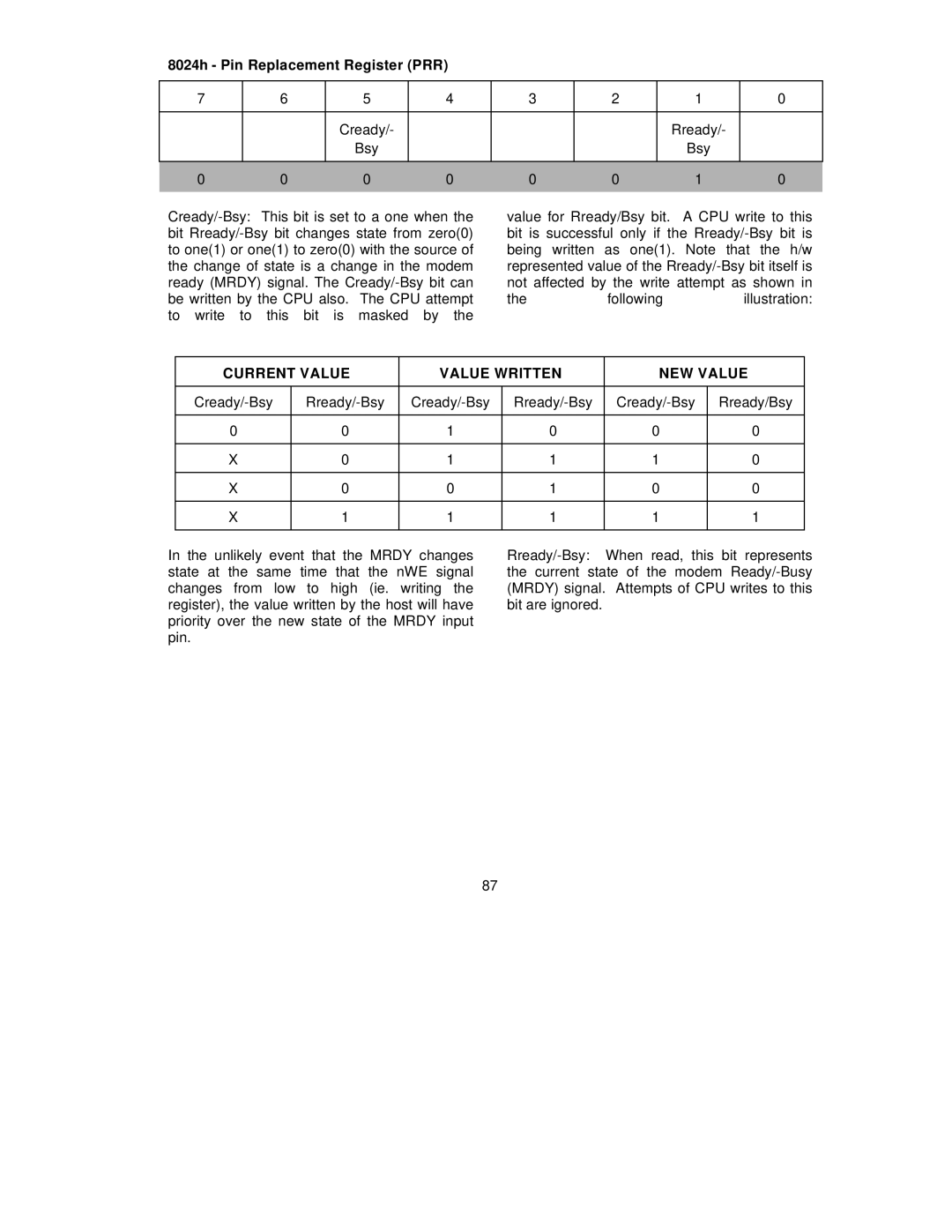

8024h - Pin Replacement Register (PRR)

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|

|

|

|

|

|

|

|

|

| Cready/- |

|

|

| Rready/- |

|

|

| Bsy |

|

|

| Bsy |

|

|

|

|

|

|

|

|

|

0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

|

|

|

|

|

|

|

|

value for Rready/Bsy bit. A CPU write to this bit is successful only if the

the | following | illustration: |

CURRENT VALUE | VALUE WRITTEN | NEW VALUE | |||

|

|

|

|

|

|

Rready/Bsy | |||||

|

|

|

|

|

|

0 | 0 | 1 | 0 | 0 | 0 |

|

|

|

|

|

|

X | 0 | 1 | 1 | 1 | 0 |

|

|

|

|

|

|

X | 0 | 0 | 1 | 0 | 0 |

|

|

|

|

|

|

X | 1 | 1 | 1 | 1 | 1 |

|

|

|

|

|

|

In the unlikely event that the MRDY changes state at the same time that the nWE signal changes from low to high (ie. writing the register), the value written by the host will have priority over the new state of the MRDY input pin.

87