I/O SPACE - BANK0 |

|

| |

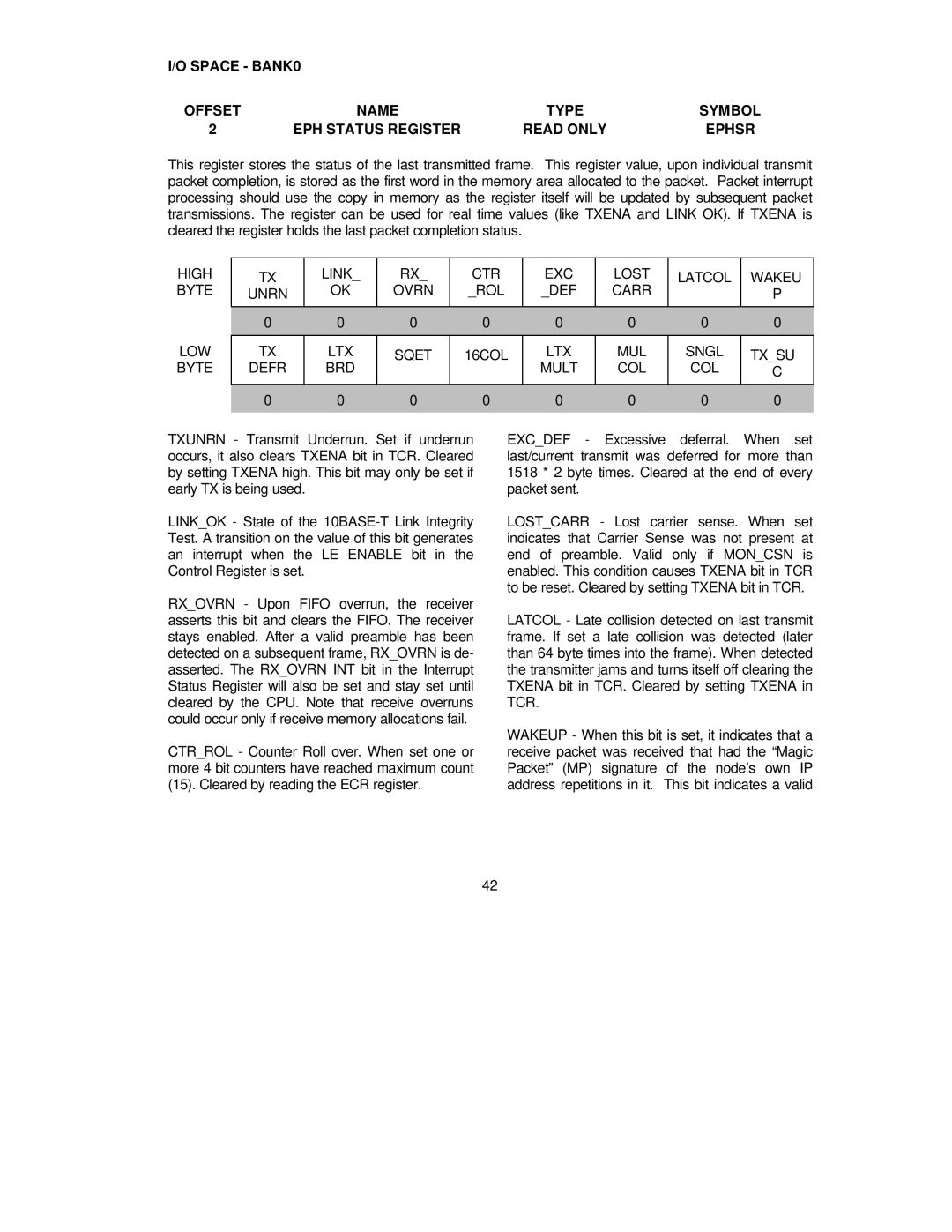

OFFSET | NAME | TYPE | SYMBOL |

2 | EPH STATUS REGISTER | READ ONLY | EPHSR |

This register stores the status of the last transmitted frame. This register value, upon individual transmit packet completion, is stored as the first word in the memory area allocated to the packet. Packet interrupt processing should use the copy in memory as the register itself will be updated by subsequent packet transmissions. The register can be used for real time values (like TXENA and LINK OK). If TXENA is cleared the register holds the last packet completion status.

HIGH | TX | LINK_ | RX_ | CTR | EXC | LOST | LATCOL | WAKEU |

BYTE | UNRN | OK | OVRN | _ROL | _DEF | CARR |

| P |

|

|

|

|

|

|

|

|

|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

LOW | TX | LTX | SQET | 16COL | LTX | MUL | SNGL | TX_SU |

BYTE | DEFR | BRD |

|

| MULT | COL | COL | C |

|

|

|

|

|

|

|

|

|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|

|

|

|

|

|

|

|

|

TXUNRN - Transmit Underrun. Set if underrun occurs, it also clears TXENA bit in TCR. Cleared by setting TXENA high. This bit may only be set if early TX is being used.

LINK_OK - State of the

RX_OVRN - Upon FIFO overrun, the receiver asserts this bit and clears the FIFO. The receiver stays enabled. After a valid preamble has been detected on a subsequent frame, RX_OVRN is de- asserted. The RX_OVRN INT bit in the Interrupt Status Register will also be set and stay set until cleared by the CPU. Note that receive overruns could occur only if receive memory allocations fail.

CTR_ROL - Counter Roll over. When set one or more 4 bit counters have reached maximum count (15). Cleared by reading the ECR register.

EXC_DEF - Excessive deferral. When set last/current transmit was deferred for more than 1518 * 2 byte times. Cleared at the end of every packet sent.

LOST_CARR - Lost carrier sense. When set indicates that Carrier Sense was not present at end of preamble. Valid only if MON_CSN is enabled. This condition causes TXENA bit in TCR to be reset. Cleared by setting TXENA bit in TCR.

LATCOL - Late collision detected on last transmit frame. If set a late collision was detected (later than 64 byte times into the frame). When detected the transmitter jams and turns itself off clearing the TXENA bit in TCR. Cleared by setting TXENA in TCR.

WAKEUP - When this bit is set, it indicates that a receive packet was received that had the “Magic Packet” (MP) signature of the node’s own IP address repetitions in it. This bit indicates a valid

42