I/O SPACE - BANK2 |

|

|

|

|

|

|

|

|

|

| |

OFFSET |

| NAME |

|

|

|

| TYPE | SYMBOL | |||

C | INTERRUPT STATUS REGISTER |

| READ ONLY |

|

| IST | |||||

|

|

|

|

|

|

|

|

|

|

|

|

| ERCV | EPH INT |

| RX_OVR |

| ALLOC |

| TX | TX INT |

| RCV INT |

| INT |

|

| N INT |

| INT |

| EMPTY |

|

|

|

|

|

|

|

|

|

|

| INT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X | 0 | 0 |

| 0 |

| 0 | 1 | 0 | 0 | ||

OFFSET |

| NAME |

|

|

|

| TYPE | SYMBOL | |||

C | INTERRUPT ACKNOWLEDGE |

| WRITE ONLY |

| ACK | ||||||

|

| REGISTER |

|

|

|

|

|

| |||

ERCV

INT

RX_OVR

N INT

TX

EMPTY

INT

TX INT

OFFSET |

| NAME |

|

|

| TYPE | SYMBOL | |||

D | INTERRUPT MASK REGISTER | READ/WRITE |

| MSK | ||||||

|

|

|

|

|

|

|

|

|

|

|

| ERCV | EPH INT |

| RX_OVR |

| ALLOC | TX | TX INT |

| RCV INT |

| INT |

|

| N INT |

| INT | EMPTY |

|

|

|

|

|

|

|

|

|

| INT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X | 0 | 0 |

| 0 |

| 0 | 0 | 0 | 0 | |

|

|

|

|

|

|

|

|

|

|

|

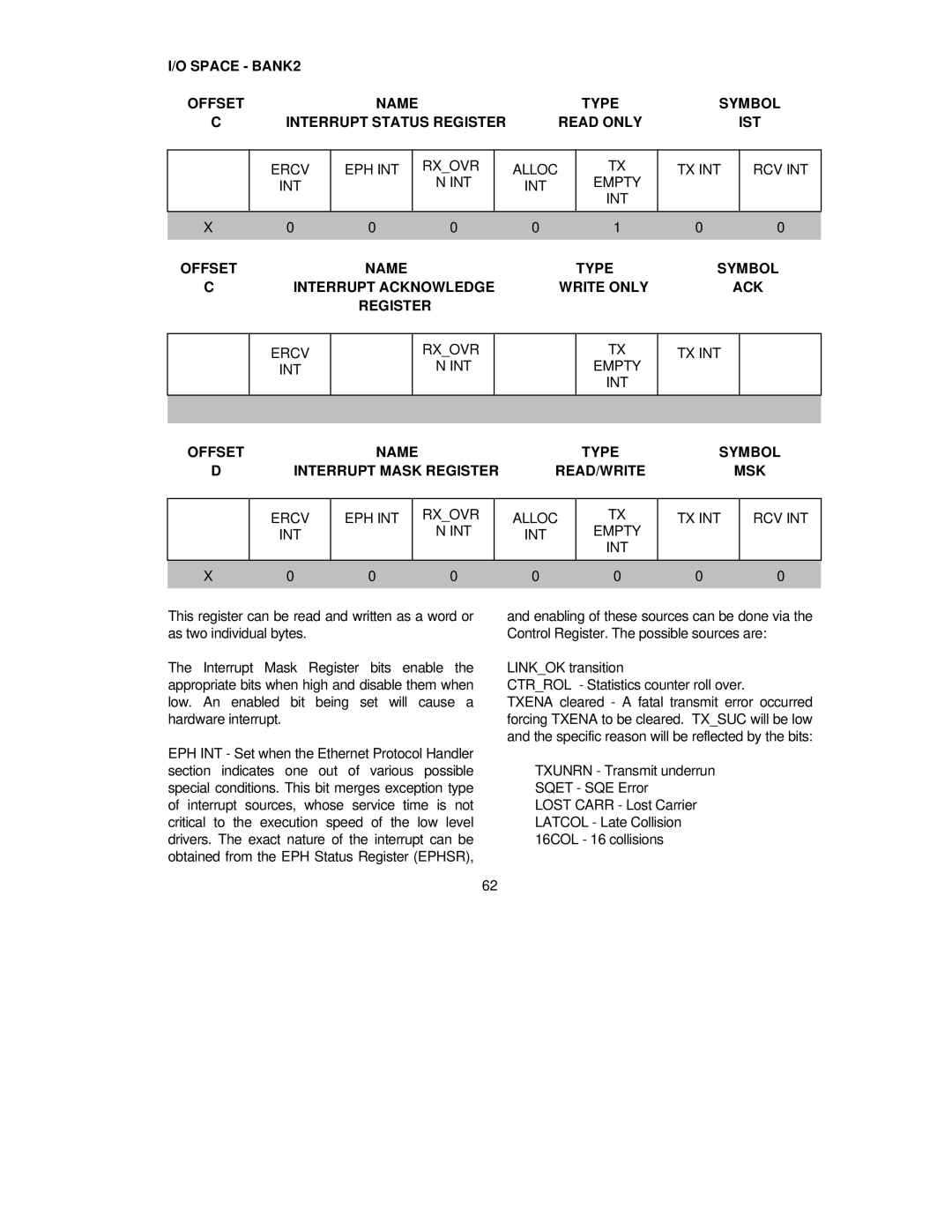

This register can be read and written as a word or as two individual bytes.

The Interrupt Mask Register bits enable the appropriate bits when high and disable them when low. An enabled bit being set will cause a hardware interrupt.

EPH INT - Set when the Ethernet Protocol Handler section indicates one out of various possible special conditions. This bit merges exception type of interrupt sources, whose service time is not critical to the execution speed of the low level drivers. The exact nature of the interrupt can be obtained from the EPH Status Register (EPHSR),

62

and enabling of these sources can be done via the Control Register. The possible sources are:

LINK_OK transition

CTR_ROL - Statistics counter roll over.

TXENA cleared - A fatal transmit error occurred forcing TXENA to be cleared. TX_SUC will be low and the specific reason will be reflected by the bits:

TXUNRN - Transmit underrun SQET - SQE Error

LOST CARR - Lost Carrier LATCOL - Late Collision 16COL - 16 collisions