I/O SPACE - BANK1 |

|

|

|

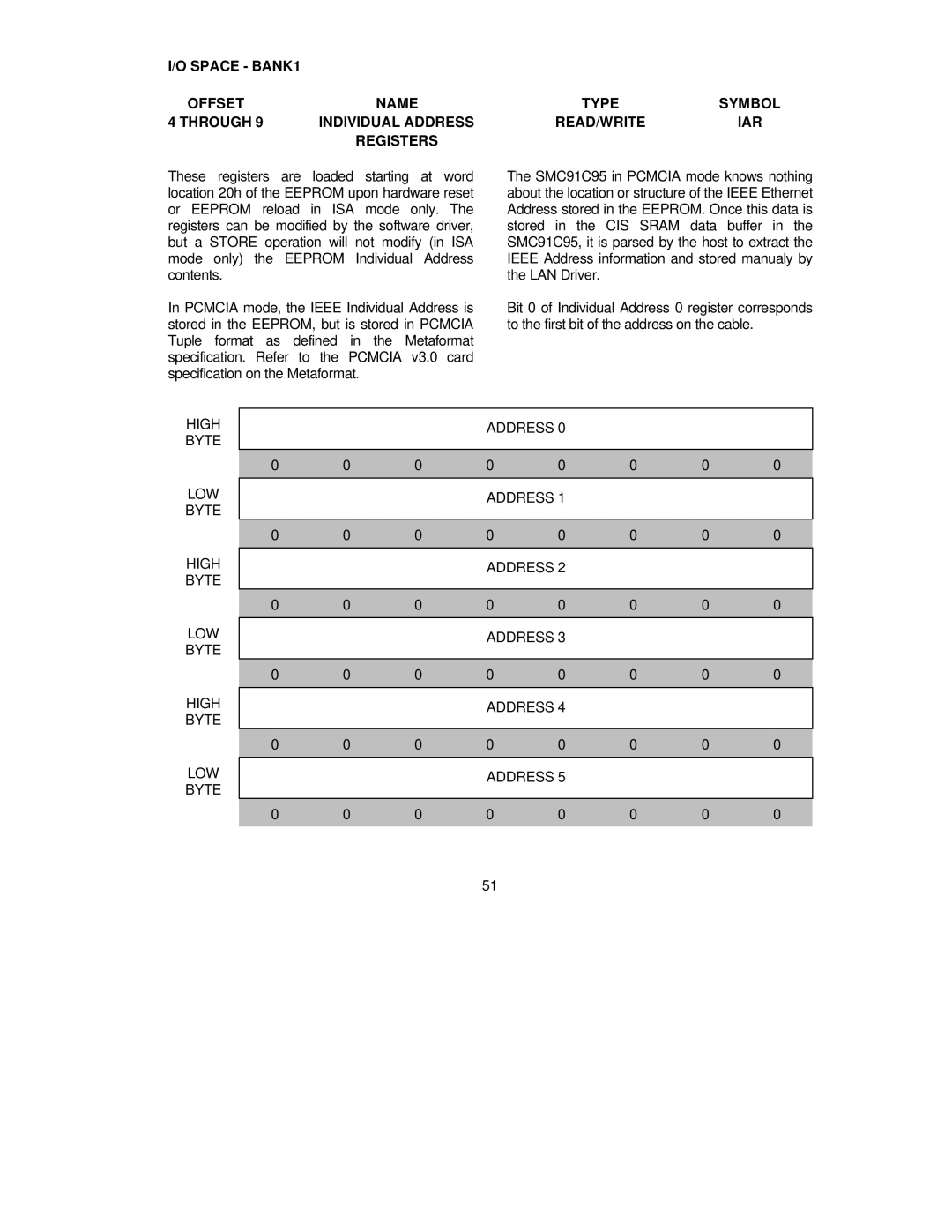

OFFSET | NAME | TYPE | SYMBOL |

4 THROUGH 9 | INDIVIDUAL ADDRESS | READ/WRITE | IAR |

| REGISTERS |

|

|

These registers are loaded starting at word location 20h of the EEPROM upon hardware reset or EEPROM reload in ISA mode only. The registers can be modified by the software driver, but a STORE operation will not modify (in ISA mode only) the EEPROM Individual Address contents.

In PCMCIA mode, the IEEE Individual Address is stored in the EEPROM, but is stored in PCMCIA Tuple format as defined in the Metaformat specification. Refer to the PCMCIA v3.0 card specification on the Metaformat.

The SMC91C95 in PCMCIA mode knows nothing about the location or structure of the IEEE Ethernet Address stored in the EEPROM. Once this data is stored in the CIS SRAM data buffer in the SMC91C95, it is parsed by the host to extract the IEEE Address information and stored manualy by the LAN Driver.

Bit 0 of Individual Address 0 register corresponds to the first bit of the address on the cable.

HIGH |

|

|

| ADDRESS 0 |

|

|

| |

BYTE |

|

|

|

|

|

|

|

|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

LOW |

|

|

| ADDRESS 1 |

|

|

| |

BYTE |

|

|

|

|

|

|

|

|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

HIGH |

|

|

| ADDRESS 2 |

|

|

| |

BYTE |

|

|

|

|

|

|

|

|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

LOW |

|

|

| ADDRESS 3 |

|

|

| |

BYTE |

|

|

|

|

|

|

|

|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

HIGH |

|

|

| ADDRESS 4 |

|

|

| |

BYTE |

|

|

|

|

|

|

|

|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

LOW |

|

|

| ADDRESS 5 |

|

|

| |

BYTE |

|

|

|

|

|

|

|

|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|

|

|

| 51 |

|

|

|

|