EMAC Module Registers | www.ti.com |

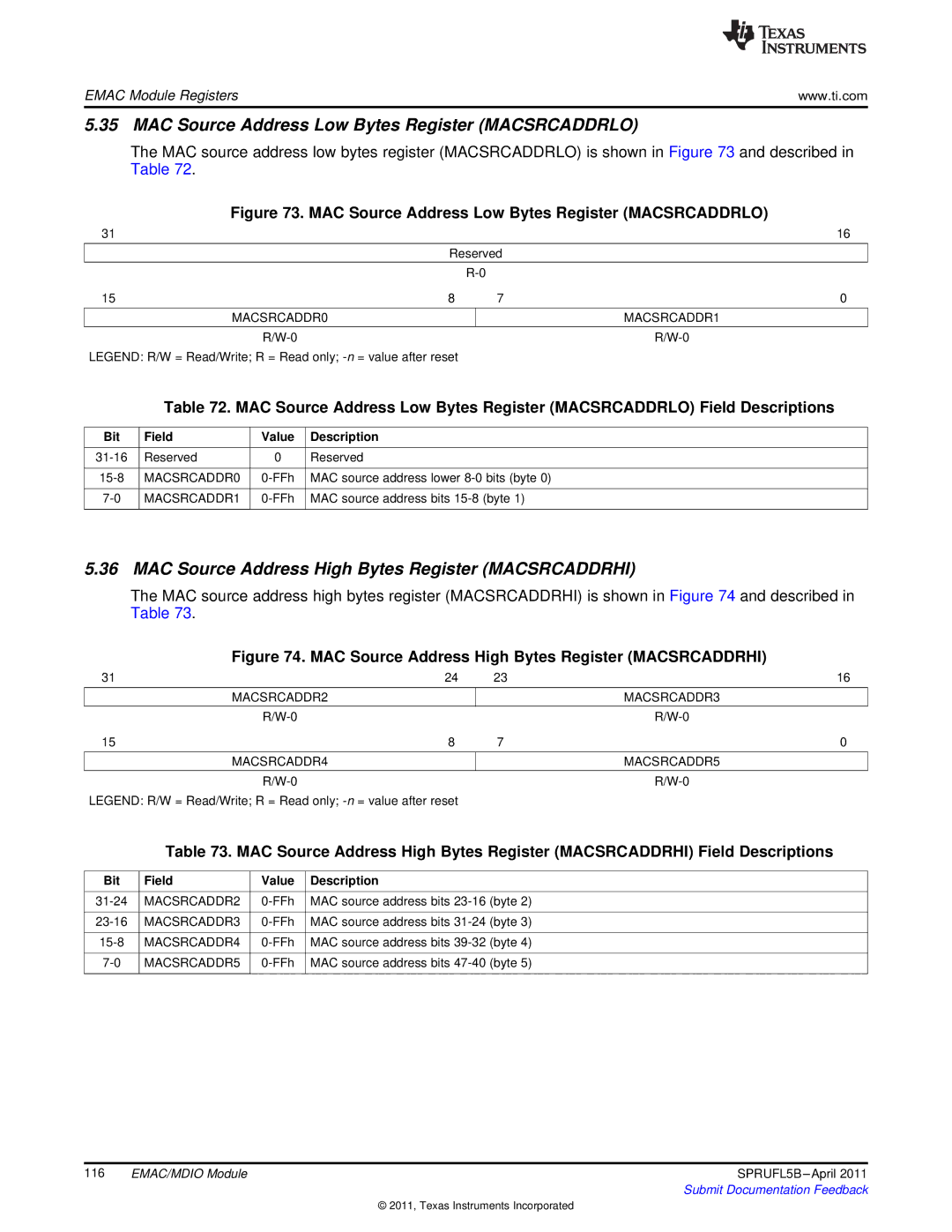

5.35 MAC Source Address Low Bytes Register (MACSRCADDRLO)

The MAC source address low bytes register (MACSRCADDRLO) is shown in Figure 73 and described in Table 72.

Figure 73. MAC Source Address Low Bytes Register (MACSRCADDRLO)

31 |

|

|

| 16 |

| Reserved |

| ||

|

|

|

| |

|

|

| ||

15 | 8 | 7 | 0 | |

|

|

|

|

|

| MACSRCADDR0 |

|

| MACSRCADDR1 |

|

|

|

|

|

|

|

| ||

LEGEND: R/W = Read/Write; R = Read only;

Table 72. MAC Source Address Low Bytes Register (MACSRCADDRLO) Field Descriptions

Bit | Field | Value | Description |

|

|

|

|

Reserved | 0 | Reserved | |

|

|

|

|

MACSRCADDR0 | MAC source address lower | ||

|

|

|

|

MACSRCADDR1 | MAC source address bits | ||

|

|

|

|

5.36 MAC Source Address High Bytes Register (MACSRCADDRHI)

The MAC source address high bytes register (MACSRCADDRHI) is shown in Figure 74 and described in Table 73.

Figure 74. MAC Source Address High Bytes Register (MACSRCADDRHI)

31 | 24 | 23 | 16 |

| MACSRCADDR2 |

| MACSRCADDR3 |

|

| ||

15 | 8 | 7 | 0 |

|

|

|

|

| MACSRCADDR4 |

| MACSRCADDR5 |

|

|

LEGEND: R/W = Read/Write; R = Read only;

Table 73. MAC Source Address High Bytes Register (MACSRCADDRHI) Field Descriptions

Bit | Field | Value | Description |

|

|

|

|

MACSRCADDR2 | MAC source address bits | ||

|

|

|

|

MACSRCADDR3 | MAC source address bits | ||

|

|

|

|

MACSRCADDR4 | MAC source address bits | ||

|

|

|

|

MACSRCADDR5 | MAC source address bits | ||

|

|

|

|

116 | EMAC/MDIO Module | SPRUFL5B |

|

| Submit Documentation Feedback |

© 2011, Texas Instruments Incorporated