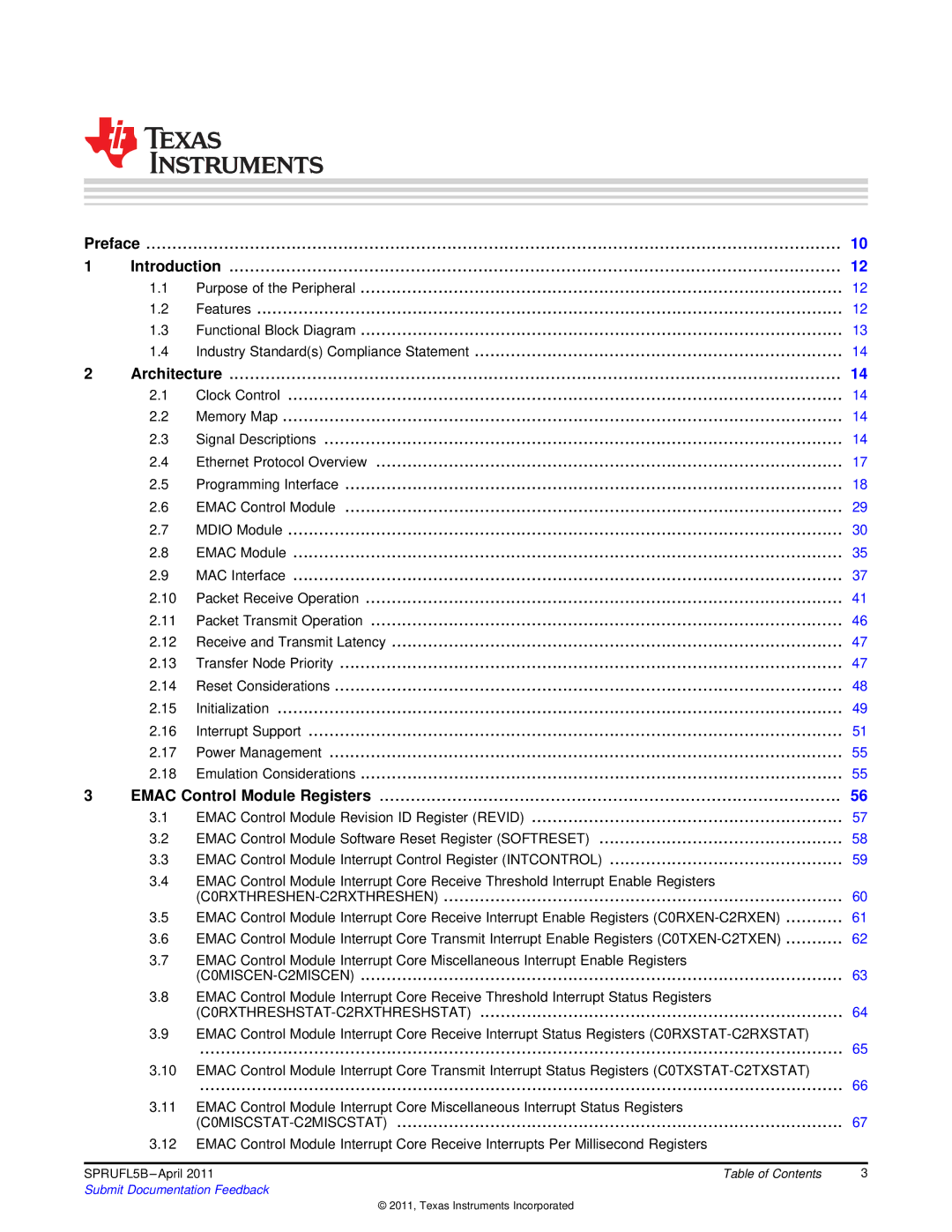

Preface | 10 | ||

1 | Introduction | 12 | |

| 1.1 | Purpose of the Peripheral | 12 |

| 1.2 | Features | 12 |

| 1.3 | Functional Block Diagram | 13 |

| 1.4 | Industry Standard(s) Compliance Statement | 14 |

2 | Architecture | 14 | |

| 2.1 | Clock Control | 14 |

| 2.2 | Memory Map | 14 |

| 2.3 | Signal Descriptions | 14 |

| 2.4 | Ethernet Protocol Overview | 17 |

| 2.5 | Programming Interface | 18 |

| 2.6 | EMAC Control Module | 29 |

| 2.7 | MDIO Module | 30 |

| 2.8 | EMAC Module | 35 |

| 2.9 | MAC Interface | 37 |

| 2.10 | Packet Receive Operation | 41 |

| 2.11 | Packet Transmit Operation | 46 |

| 2.12 | Receive and Transmit Latency | 47 |

| 2.13 | Transfer Node Priority | 47 |

| 2.14 | Reset Considerations | 48 |

| 2.15 | Initialization | 49 |

| 2.16 | Interrupt Support | 51 |

| 2.17 | Power Management | 55 |

| 2.18 | Emulation Considerations | 55 |

3 | EMAC Control Module Registers | 56 | |

| 3.1 | EMAC Control Module Revision ID Register (REVID) | 57 |

| 3.2 | EMAC Control Module Software Reset Register (SOFTRESET) | 58 |

| 3.3 | EMAC Control Module Interrupt Control Register (INTCONTROL) | 59 |

3.4EMAC Control Module Interrupt Core Receive Threshold Interrupt Enable Registers

|

| 60 |

3.5 | EMAC Control Module Interrupt Core Receive Interrupt Enable Registers | 61 |

3.6 | EMAC Control Module Interrupt Core Transmit Interrupt Enable Registers | 62 |

3.7EMAC Control Module Interrupt Core Miscellaneous Interrupt Enable Registers

| 63 |

3.8EMAC Control Module Interrupt Core Receive Threshold Interrupt Status Registers

| 64 |

3.9EMAC Control Module Interrupt Core Receive Interrupt Status Registers

............................................................................................................................ 65

3.10EMAC Control Module Interrupt Core Transmit Interrupt Status Registers

............................................................................................................................ 66

3.11EMAC Control Module Interrupt Core Miscellaneous Interrupt Status Registers

| 67 |

3.12EMAC Control Module Interrupt Core Receive Interrupts Per Millisecond Registers

SPRUFL5B | Table of Contents | 3 |

Submit Documentation Feedback |

|

|

© 2011, Texas Instruments Incorporated