EMAC Control Module Registers | www.ti.com |

3.2EMAC Control Module Software Reset Register (SOFTRESET)

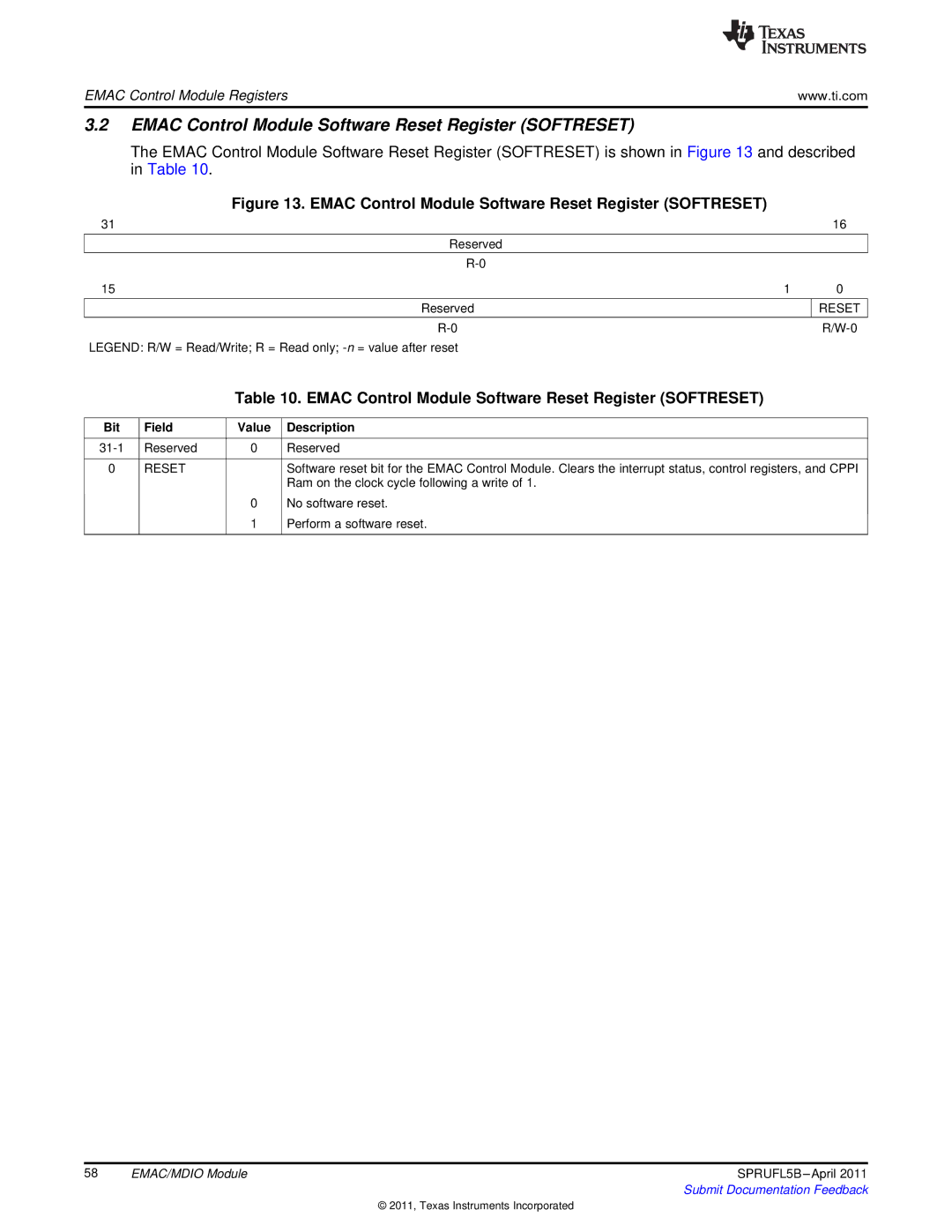

The EMAC Control Module Software Reset Register (SOFTRESET) is shown in Figure 13 and described in Table 10.

Figure 13. EMAC Control Module Software Reset Register (SOFTRESET)

31 |

| 16 |

Reserved |

|

|

|

|

|

|

| |

15 | 1 | 0 |

|

|

|

Reserved |

| RESET |

|

|

|

|

LEGEND: R/W = Read/Write; R = Read only;

Table 10. EMAC Control Module Software Reset Register (SOFTRESET)

Bit | Field | Value | Description |

|

|

|

|

Reserved | 0 | Reserved | |

|

|

|

|

0 | RESET |

| Software reset bit for the EMAC Control Module. Clears the interrupt status, control registers, and CPPI |

|

|

| Ram on the clock cycle following a write of 1. |

|

| 0 | No software reset. |

|

| 1 | Perform a software reset. |

|

|

|

|

58 | EMAC/MDIO Module | SPRUFL5B |

|

| Submit Documentation Feedback |

© 2011, Texas Instruments Incorporated