EMAC Control Module Registers | www.ti.com |

3.12EMAC Control Module Interrupt Core Receive Interrupts Per Millisecond Registers

The EMAC control module interrupt core

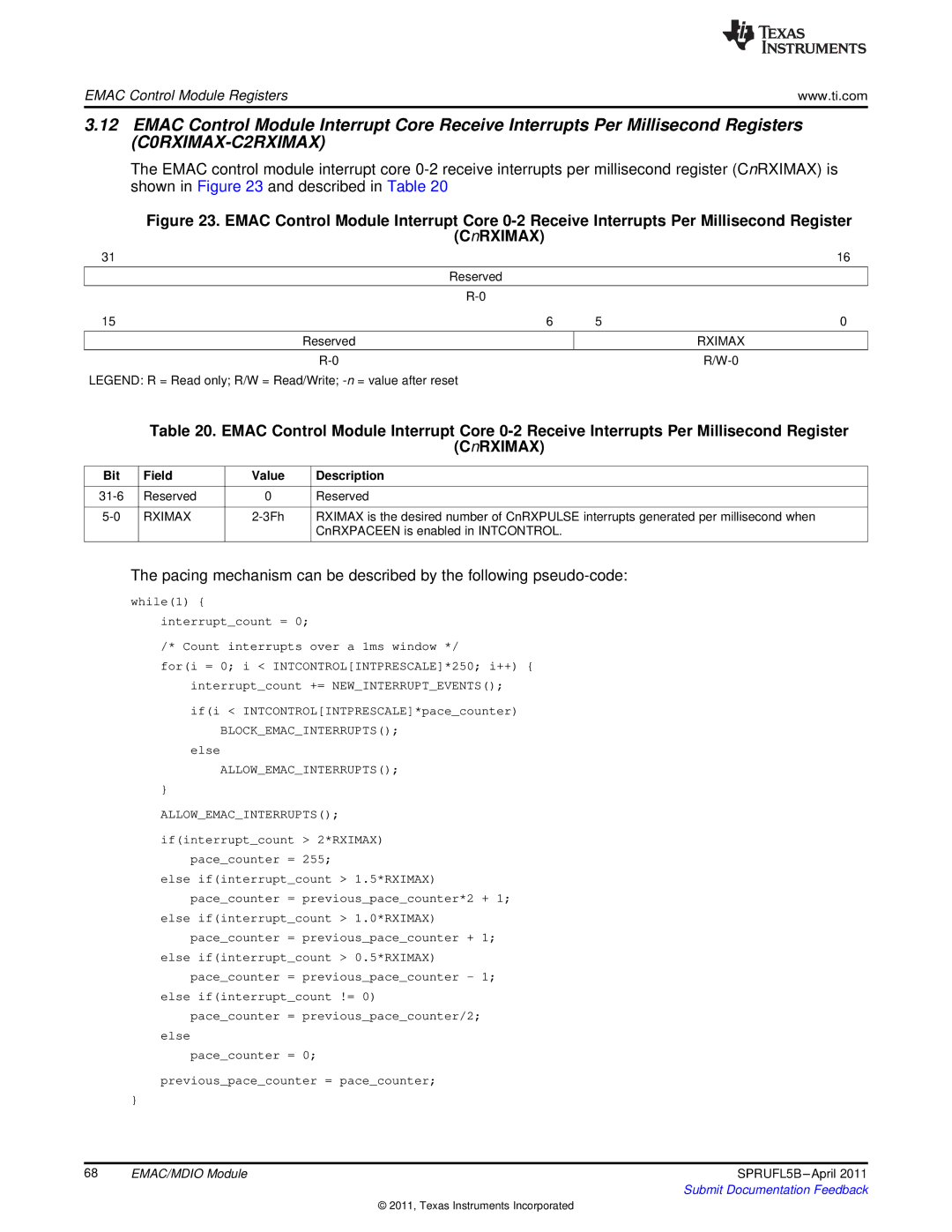

Figure 23. EMAC Control Module Interrupt Core 0-2 Receive Interrupts Per Millisecond Register

(CnRXIMAX)

31 |

|

| 16 |

| Reserved |

|

|

|

|

|

|

|

|

| |

15 | 6 | 5 | 0 |

|

|

|

|

Reserved |

|

| RXIMAX |

|

|

|

|

|

|

LEGEND: R = Read only; R/W = Read/Write;

Table 20. EMAC Control Module Interrupt Core

(CnRXIMAX)

Bit | Field | Value | Description |

|

|

|

|

Reserved | 0 | Reserved | |

|

|

|

|

RXIMAX | RXIMAX is the desired number of CnRXPULSE interrupts generated per millisecond when | ||

|

|

| CnRXPACEEN is enabled in INTCONTROL. |

|

|

|

|

The pacing mechanism can be described by the following

while(1) { interrupt_count = 0;

/* Count interrupts over a 1ms window */

for(i = 0; i < INTCONTROL[INTPRESCALE]*250; i++) {

interrupt_count += NEW_INTERRUPT_EVENTS(); if(i < INTCONTROL[INTPRESCALE]*pace_counter)

BLOCK_EMAC_INTERRUPTS();

else

ALLOW_EMAC_INTERRUPTS();

}

ALLOW_EMAC_INTERRUPTS(); if(interrupt_count > 2*RXIMAX)

pace_counter = 255;

else if(interrupt_count > 1.5*RXIMAX)

pace_counter = previous_pace_counter*2 + 1;

else if(interrupt_count > 1.0*RXIMAX)

pace_counter = previous_pace_counter + 1;

else if(interrupt_count > 0.5*RXIMAX)

pace_counter = previous_pace_counter - 1;

else if(interrupt_count != 0)

pace_counter = previous_pace_counter/2;

else

pace_counter = 0;

previous_pace_counter = pace_counter;

}

68 | EMAC/MDIO Module | SPRUFL5B |

|

| Submit Documentation Feedback |

© 2011, Texas Instruments Incorporated