EMAC Module Registerswww.ti.com

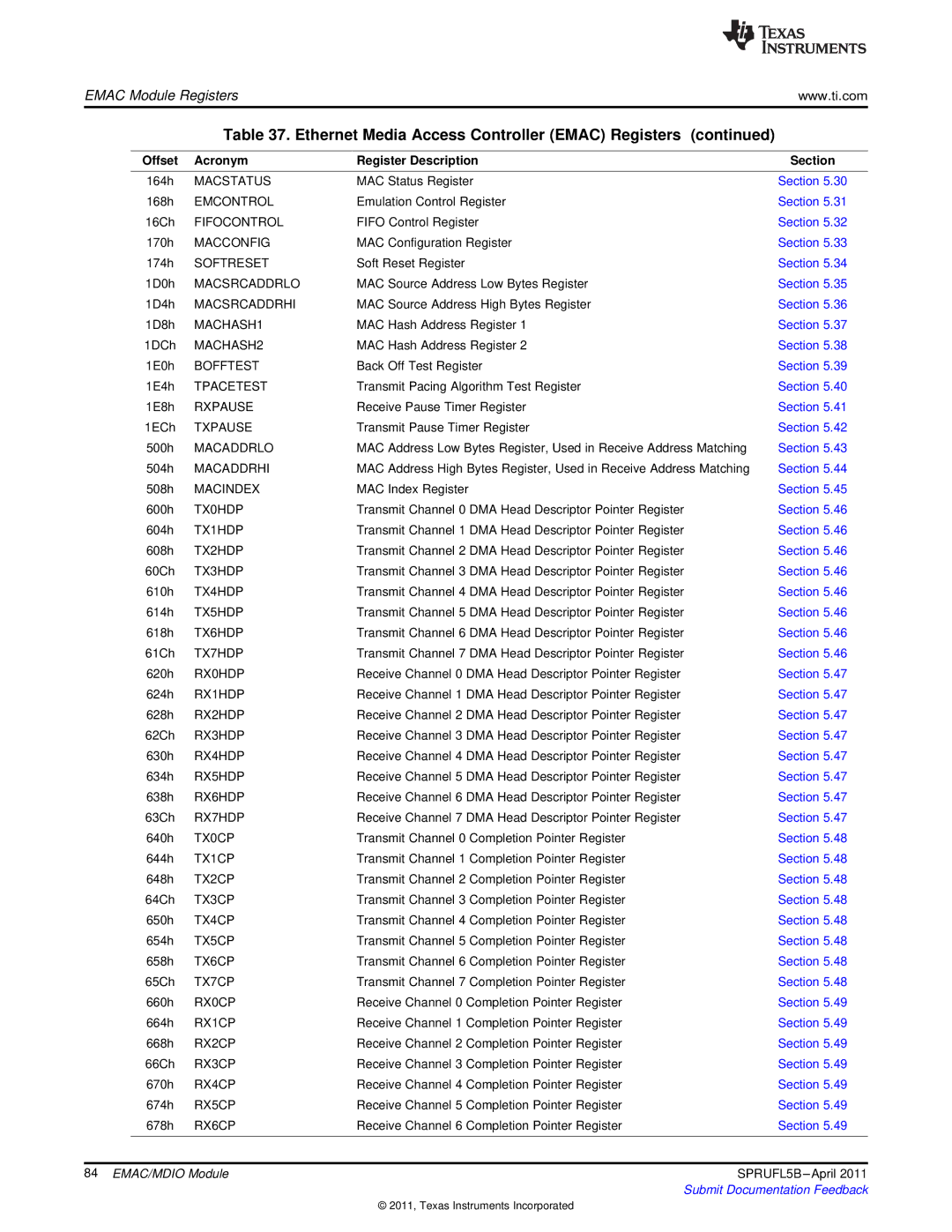

Table 37. Ethernet Media Access Controller (EMAC) Registers (continued)

| Offset | Acronym | Register Description | Section |

| 164h | MACSTATUS | MAC Status Register | Section 5.30 |

| 168h | EMCONTROL | Emulation Control Register | Section 5.31 |

| 16Ch | FIFOCONTROL | FIFO Control Register | Section 5.32 |

| 170h | MACCONFIG | MAC Configuration Register | Section 5.33 |

| 174h | SOFTRESET | Soft Reset Register | Section 5.34 |

| 1D0h | MACSRCADDRLO | MAC Source Address Low Bytes Register | Section 5.35 |

| 1D4h | MACSRCADDRHI | MAC Source Address High Bytes Register | Section 5.36 |

| 1D8h | MACHASH1 | MAC Hash Address Register 1 | Section 5.37 |

| 1DCh | MACHASH2 | MAC Hash Address Register 2 | Section 5.38 |

| 1E0h | BOFFTEST | Back Off Test Register | Section 5.39 |

| 1E4h | TPACETEST | Transmit Pacing Algorithm Test Register | Section 5.40 |

| 1E8h | RXPAUSE | Receive Pause Timer Register | Section 5.41 |

| 1ECh | TXPAUSE | Transmit Pause Timer Register | Section 5.42 |

| 500h | MACADDRLO | MAC Address Low Bytes Register, Used in Receive Address Matching | Section 5.43 |

| 504h | MACADDRHI | MAC Address High Bytes Register, Used in Receive Address Matching | Section 5.44 |

| 508h | MACINDEX | MAC Index Register | Section 5.45 |

| 600h | TX0HDP | Transmit Channel 0 DMA Head Descriptor Pointer Register | Section 5.46 |

| 604h | TX1HDP | Transmit Channel 1 DMA Head Descriptor Pointer Register | Section 5.46 |

| 608h | TX2HDP | Transmit Channel 2 DMA Head Descriptor Pointer Register | Section 5.46 |

| 60Ch | TX3HDP | Transmit Channel 3 DMA Head Descriptor Pointer Register | Section 5.46 |

| 610h | TX4HDP | Transmit Channel 4 DMA Head Descriptor Pointer Register | Section 5.46 |

| 614h | TX5HDP | Transmit Channel 5 DMA Head Descriptor Pointer Register | Section 5.46 |

| 618h | TX6HDP | Transmit Channel 6 DMA Head Descriptor Pointer Register | Section 5.46 |

| 61Ch | TX7HDP | Transmit Channel 7 DMA Head Descriptor Pointer Register | Section 5.46 |

| 620h | RX0HDP | Receive Channel 0 DMA Head Descriptor Pointer Register | Section 5.47 |

| 624h | RX1HDP | Receive Channel 1 DMA Head Descriptor Pointer Register | Section 5.47 |

| 628h | RX2HDP | Receive Channel 2 DMA Head Descriptor Pointer Register | Section 5.47 |

| 62Ch | RX3HDP | Receive Channel 3 DMA Head Descriptor Pointer Register | Section 5.47 |

| 630h | RX4HDP | Receive Channel 4 DMA Head Descriptor Pointer Register | Section 5.47 |

| 634h | RX5HDP | Receive Channel 5 DMA Head Descriptor Pointer Register | Section 5.47 |

| 638h | RX6HDP | Receive Channel 6 DMA Head Descriptor Pointer Register | Section 5.47 |

| 63Ch | RX7HDP | Receive Channel 7 DMA Head Descriptor Pointer Register | Section 5.47 |

| 640h | TX0CP | Transmit Channel 0 Completion Pointer Register | Section 5.48 |

| 644h | TX1CP | Transmit Channel 1 Completion Pointer Register | Section 5.48 |

| 648h | TX2CP | Transmit Channel 2 Completion Pointer Register | Section 5.48 |

| 64Ch | TX3CP | Transmit Channel 3 Completion Pointer Register | Section 5.48 |

| 650h | TX4CP | Transmit Channel 4 Completion Pointer Register | Section 5.48 |

| 654h | TX5CP | Transmit Channel 5 Completion Pointer Register | Section 5.48 |

| 658h | TX6CP | Transmit Channel 6 Completion Pointer Register | Section 5.48 |

| 65Ch | TX7CP | Transmit Channel 7 Completion Pointer Register | Section 5.48 |

| 660h | RX0CP | Receive Channel 0 Completion Pointer Register | Section 5.49 |

| 664h | RX1CP | Receive Channel 1 Completion Pointer Register | Section 5.49 |

| 668h | RX2CP | Receive Channel 2 Completion Pointer Register | Section 5.49 |

| 66Ch | RX3CP | Receive Channel 3 Completion Pointer Register | Section 5.49 |

| 670h | RX4CP | Receive Channel 4 Completion Pointer Register | Section 5.49 |

| 674h | RX5CP | Receive Channel 5 Completion Pointer Register | Section 5.49 |

| 678h | RX6CP | Receive Channel 6 Completion Pointer Register | Section 5.49 |

|

|

| ||

|

|

|

|

|

84 EMAC/MDIO Module | SPRUFL5B | |||

|

|

| Submit Documentation Feedback | |

© 2011, Texas Instruments Incorporated