EMAC Control Module Registers | www.ti.com |

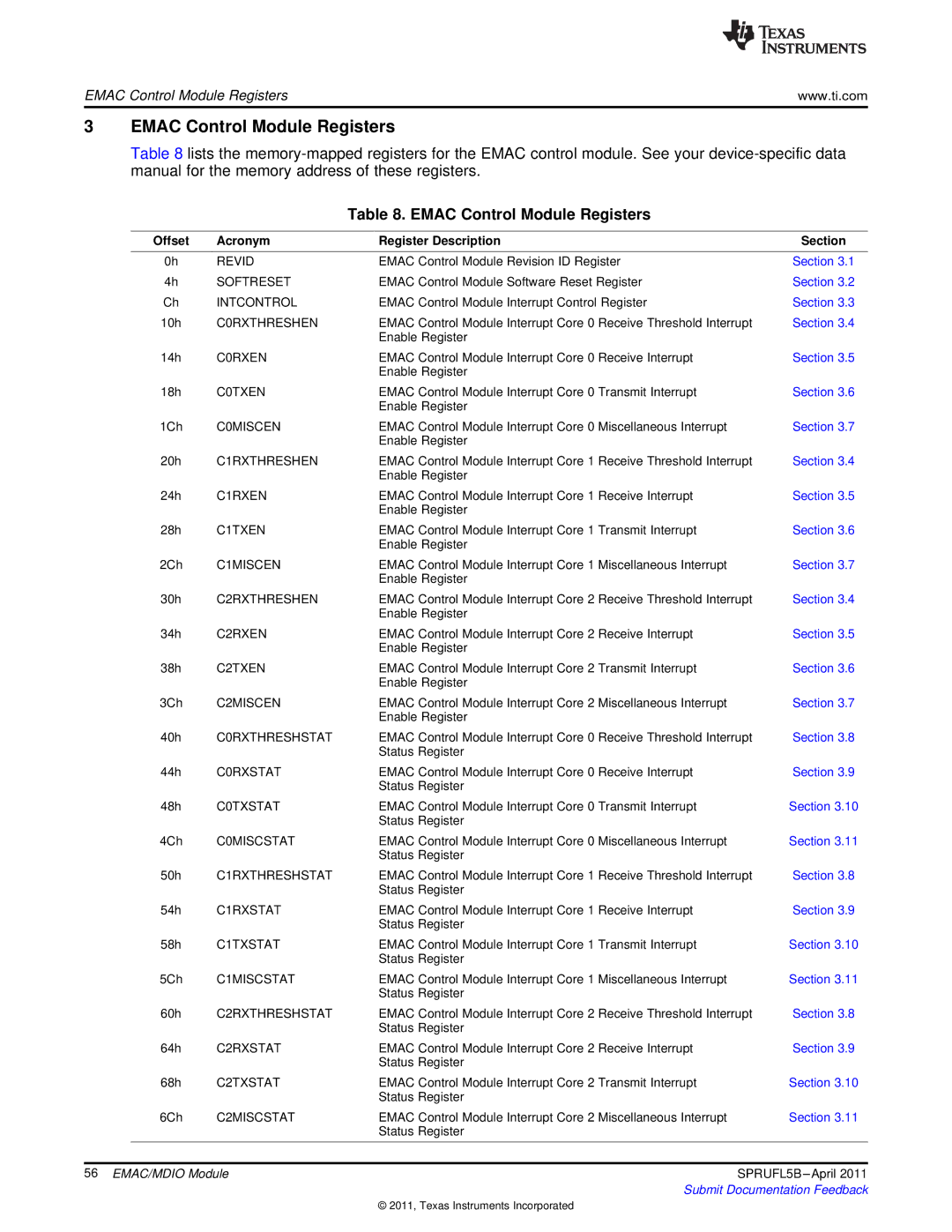

3EMAC Control Module Registers

Table 8 lists the

Table 8. EMAC Control Module Registers

| Offset | Acronym | Register Description | Section |

| 0h | REVID | EMAC Control Module Revision ID Register | Section 3.1 |

| 4h | SOFTRESET | EMAC Control Module Software Reset Register | Section 3.2 |

| Ch | INTCONTROL | EMAC Control Module Interrupt Control Register | Section 3.3 |

| 10h | C0RXTHRESHEN | EMAC Control Module Interrupt Core 0 Receive Threshold Interrupt | Section 3.4 |

|

|

| Enable Register |

|

| 14h | C0RXEN | EMAC Control Module Interrupt Core 0 Receive Interrupt | Section 3.5 |

|

|

| Enable Register |

|

| 18h | C0TXEN | EMAC Control Module Interrupt Core 0 Transmit Interrupt | Section 3.6 |

|

|

| Enable Register |

|

| 1Ch | C0MISCEN | EMAC Control Module Interrupt Core 0 Miscellaneous Interrupt | Section 3.7 |

|

|

| Enable Register |

|

| 20h | C1RXTHRESHEN | EMAC Control Module Interrupt Core 1 Receive Threshold Interrupt | Section 3.4 |

|

|

| Enable Register |

|

| 24h | C1RXEN | EMAC Control Module Interrupt Core 1 Receive Interrupt | Section 3.5 |

|

|

| Enable Register |

|

| 28h | C1TXEN | EMAC Control Module Interrupt Core 1 Transmit Interrupt | Section 3.6 |

|

|

| Enable Register |

|

| 2Ch | C1MISCEN | EMAC Control Module Interrupt Core 1 Miscellaneous Interrupt | Section 3.7 |

|

|

| Enable Register |

|

| 30h | C2RXTHRESHEN | EMAC Control Module Interrupt Core 2 Receive Threshold Interrupt | Section 3.4 |

|

|

| Enable Register |

|

| 34h | C2RXEN | EMAC Control Module Interrupt Core 2 Receive Interrupt | Section 3.5 |

|

|

| Enable Register |

|

| 38h | C2TXEN | EMAC Control Module Interrupt Core 2 Transmit Interrupt | Section 3.6 |

|

|

| Enable Register |

|

| 3Ch | C2MISCEN | EMAC Control Module Interrupt Core 2 Miscellaneous Interrupt | Section 3.7 |

|

|

| Enable Register |

|

| 40h | C0RXTHRESHSTAT | EMAC Control Module Interrupt Core 0 Receive Threshold Interrupt | Section 3.8 |

|

|

| Status Register |

|

| 44h | C0RXSTAT | EMAC Control Module Interrupt Core 0 Receive Interrupt | Section 3.9 |

|

|

| Status Register |

|

| 48h | C0TXSTAT | EMAC Control Module Interrupt Core 0 Transmit Interrupt | Section 3.10 |

|

|

| Status Register |

|

| 4Ch | C0MISCSTAT | EMAC Control Module Interrupt Core 0 Miscellaneous Interrupt | Section 3.11 |

|

|

| Status Register |

|

| 50h | C1RXTHRESHSTAT | EMAC Control Module Interrupt Core 1 Receive Threshold Interrupt | Section 3.8 |

|

|

| Status Register |

|

| 54h | C1RXSTAT | EMAC Control Module Interrupt Core 1 Receive Interrupt | Section 3.9 |

|

|

| Status Register |

|

| 58h | C1TXSTAT | EMAC Control Module Interrupt Core 1 Transmit Interrupt | Section 3.10 |

|

|

| Status Register |

|

| 5Ch | C1MISCSTAT | EMAC Control Module Interrupt Core 1 Miscellaneous Interrupt | Section 3.11 |

|

|

| Status Register |

|

| 60h | C2RXTHRESHSTAT | EMAC Control Module Interrupt Core 2 Receive Threshold Interrupt | Section 3.8 |

|

|

| Status Register |

|

| 64h | C2RXSTAT | EMAC Control Module Interrupt Core 2 Receive Interrupt | Section 3.9 |

|

|

| Status Register |

|

| 68h | C2TXSTAT | EMAC Control Module Interrupt Core 2 Transmit Interrupt | Section 3.10 |

|

|

| Status Register |

|

| 6Ch | C2MISCSTAT | EMAC Control Module Interrupt Core 2 Miscellaneous Interrupt | Section 3.11 |

|

|

| Status Register |

|

|

|

| ||

|

|

|

|

|

56 EMAC/MDIO Module | SPRUFL5B | |||

|

|

| Submit Documentation Feedback | |

© 2011, Texas Instruments Incorporated