www.ti.com | EMAC Module Registers |

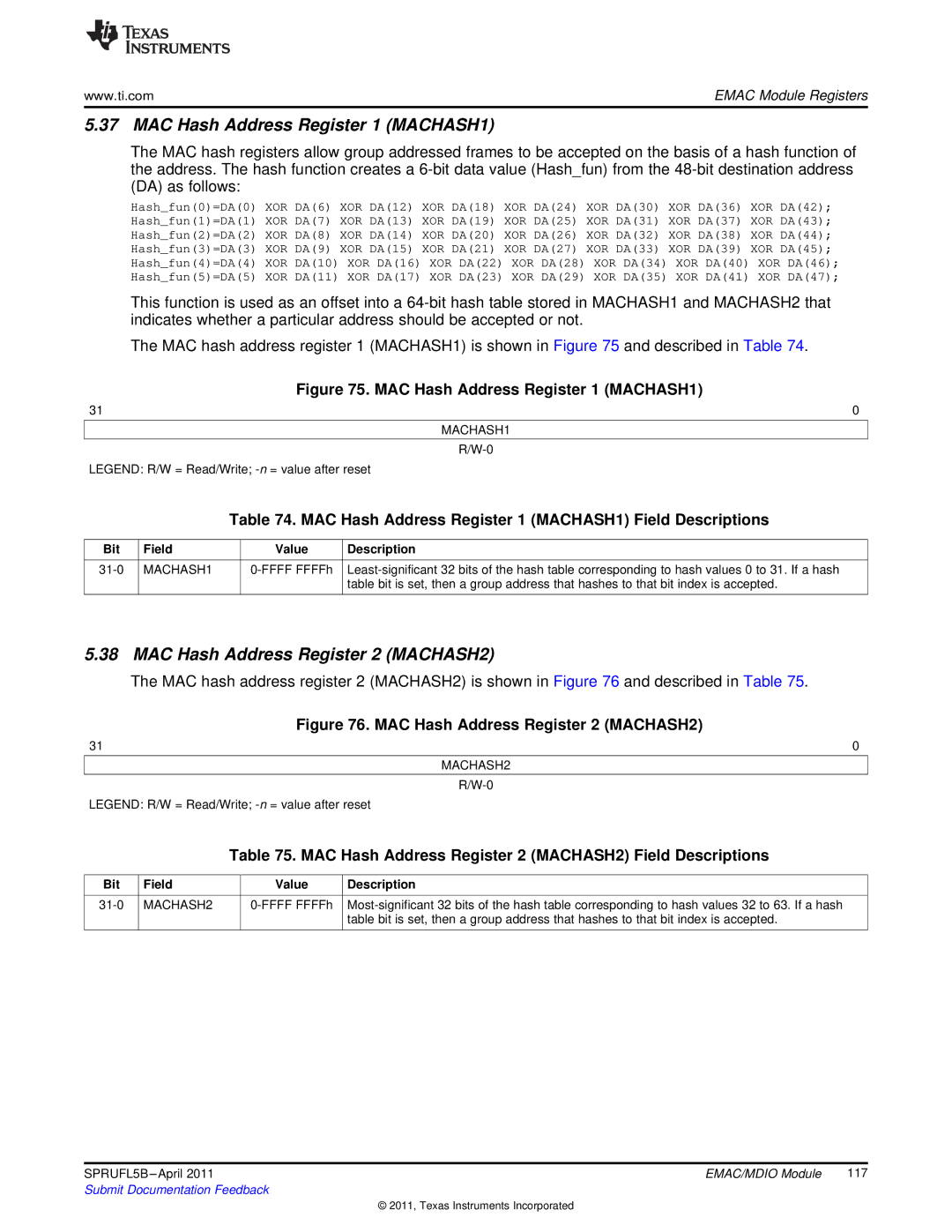

5.37 MAC Hash Address Register 1 (MACHASH1)

The MAC hash registers allow group addressed frames to be accepted on the basis of a hash function of the address. The hash function creates a

Hash_fun(0)=DA(0) XOR DA(6) XOR DA(12) XOR DA(18) XOR DA(24) XOR DA(30) XOR DA(36) XOR DA(42); Hash_fun(1)=DA(1) XOR DA(7) XOR DA(13) XOR DA(19) XOR DA(25) XOR DA(31) XOR DA(37) XOR DA(43); Hash_fun(2)=DA(2) XOR DA(8) XOR DA(14) XOR DA(20) XOR DA(26) XOR DA(32) XOR DA(38) XOR DA(44); Hash_fun(3)=DA(3) XOR DA(9) XOR DA(15) XOR DA(21) XOR DA(27) XOR DA(33) XOR DA(39) XOR DA(45); Hash_fun(4)=DA(4) XOR DA(10) XOR DA(16) XOR DA(22) XOR DA(28) XOR DA(34) XOR DA(40) XOR DA(46); Hash_fun(5)=DA(5) XOR DA(11) XOR DA(17) XOR DA(23) XOR DA(29) XOR DA(35) XOR DA(41) XOR DA(47);

This function is used as an offset into a

The MAC hash address register 1 (MACHASH1) is shown in Figure 75 and described in Table 74.

Figure 75. MAC Hash Address Register 1 (MACHASH1)

31 | 0 |

MACHASH1

LEGEND: R/W = Read/Write;

Table 74. MAC Hash Address Register 1 (MACHASH1) Field Descriptions

Bit | Field | Value | Description |

|

|

|

|

MACHASH1 | |||

|

|

| table bit is set, then a group address that hashes to that bit index is accepted. |

|

|

|

|

5.38 MAC Hash Address Register 2 (MACHASH2)

The MAC hash address register 2 (MACHASH2) is shown in Figure 76 and described in Table 75.

Figure 76. MAC Hash Address Register 2 (MACHASH2)

31 | 0 |

MACHASH2

LEGEND: R/W = Read/Write;

Table 75. MAC Hash Address Register 2 (MACHASH2) Field Descriptions

Bit | Field | Value | Description |

|

|

|

|

MACHASH2 | |||

|

|

| table bit is set, then a group address that hashes to that bit index is accepted. |

|

|

|

|

SPRUFL5B | EMAC/MDIO Module | 117 |

Submit Documentation Feedback |

|

|

© 2011, Texas Instruments Incorporated