www.ti.comEMAC Control Module Registers

Table 8. EMAC Control Module Registers (continued)

Offset | Acronym | Register Description | Section |

70h | C0RXIMAX | EMAC Control Module Interrupt Core 0 Receive Interrupts Per | Section 3.12 |

|

| Millisecond Register |

|

74h | C0TXIMAX | EMAC Control Module Interrupt Core 0 Transmit Interrupts Per | Section 3.13 |

|

| Millisecond Register |

|

78h | C1RXIMAX | EMAC Control Module Interrupt Core 1 Receive Interrupts Per | Section 3.12 |

|

| Millisecond Register |

|

7Ch | C1TXIMAX | EMAC Control Module Interrupt Core 1 Transmit Interrupts Per | Section 3.13 |

|

| Millisecond Register |

|

80h | C2RXIMAX | EMAC Control Module Interrupt Core 2 Receive Interrupts Per | Section 3.12 |

|

| Millisecond Register |

|

84h | C2TXIMAX | EMAC Control Module Interrupt Core 2 Transmit Interrupts Per | Section 3.13 |

|

| Millisecond Register |

|

|

|

|

|

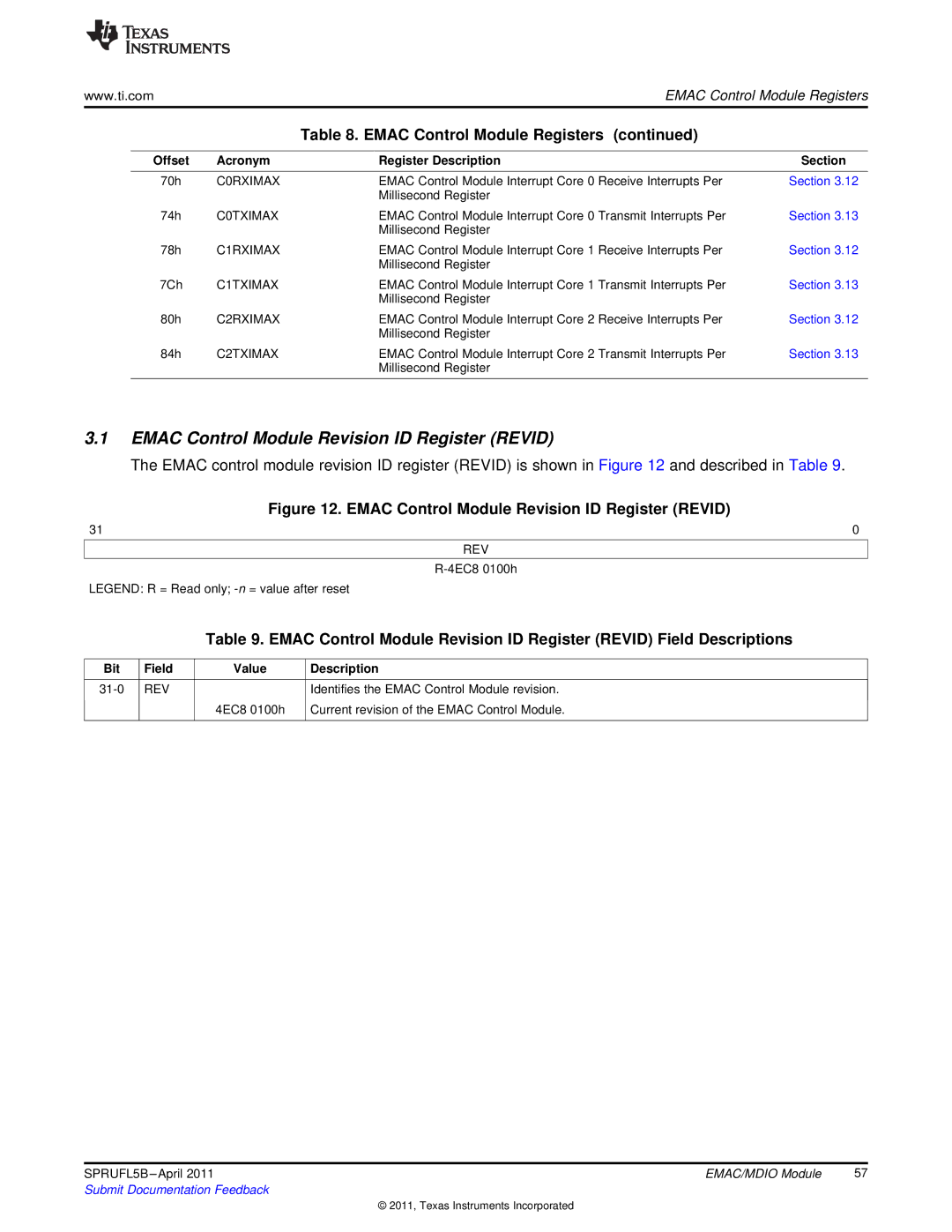

3.1EMAC Control Module Revision ID Register (REVID)

The EMAC control module revision ID register (REVID) is shown in Figure 12 and described in Table 9.

Figure 12. EMAC Control Module Revision ID Register (REVID)

31 | 0 |

REV

LEGEND: R = Read only;

Table 9. EMAC Control Module Revision ID Register (REVID) Field Descriptions

Bit | Field | Value | Description |

|

|

|

|

REV |

| Identifies the EMAC Control Module revision. | |

|

| 4EC8 0100h | Current revision of the EMAC Control Module. |

|

|

|

|

SPRUFL5B | EMAC/MDIO Module | 57 |

Submit Documentation Feedback |

|

|

© 2011, Texas Instruments Incorporated