www.ti.com | EMAC Module Registers |

5.8Transmit Interrupt Status (Masked) Register (TXINTSTATMASKED)

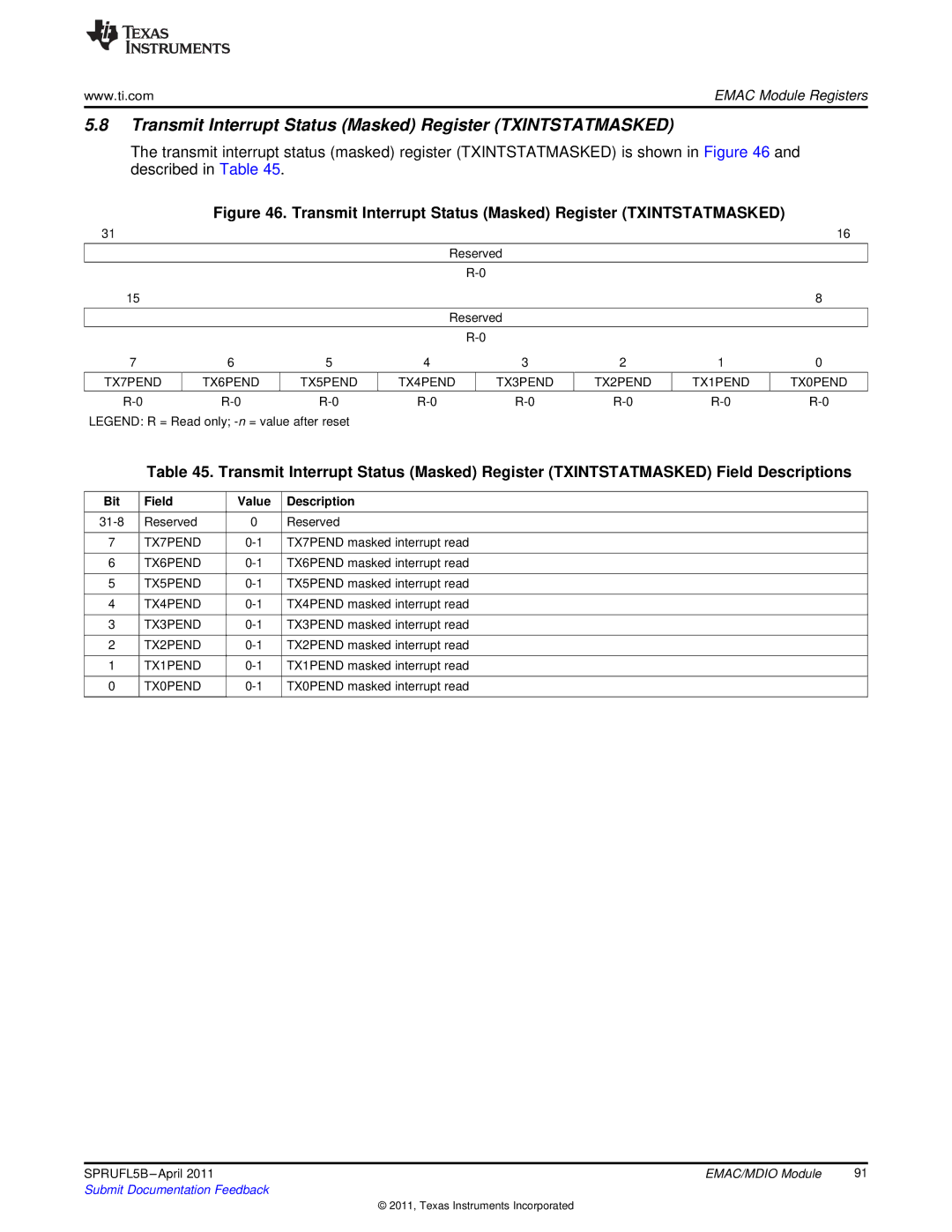

The transmit interrupt status (masked) register (TXINTSTATMASKED) is shown in Figure 46 and described in Table 45.

| Figure 46. Transmit Interrupt Status (Masked) Register (TXINTSTATMASKED) |

| |||||||

31 |

|

|

|

|

|

|

|

| 16 |

|

|

|

|

|

|

|

| ||

|

|

| Reserved |

|

|

|

| ||

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| ||

15 |

|

|

|

|

|

|

|

| 8 |

|

|

|

|

|

|

|

| ||

|

|

| Reserved |

|

|

|

| ||

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| ||

7 | 6 | 5 | 4 | 3 | 2 | 1 |

| 0 | |

|

|

|

|

|

|

|

|

| |

TX7PEND | TX6PEND | TX5PEND | TX4PEND |

| TX3PEND | TX2PEND | TX1PEND |

| TX0PEND |

|

|

|

|

|

|

|

|

|

|

| |||||||||

LEGEND: R = Read only;

Table 45. Transmit Interrupt Status (Masked) Register (TXINTSTATMASKED) Field Descriptions

Bit | Field | Value | Description |

|

|

|

|

Reserved | 0 | Reserved | |

|

|

|

|

7 | TX7PEND | TX7PEND masked interrupt read | |

|

|

|

|

6 | TX6PEND | TX6PEND masked interrupt read | |

|

|

|

|

5 | TX5PEND | TX5PEND masked interrupt read | |

|

|

|

|

4 | TX4PEND | TX4PEND masked interrupt read | |

|

|

|

|

3 | TX3PEND | TX3PEND masked interrupt read | |

|

|

|

|

2 | TX2PEND | TX2PEND masked interrupt read | |

|

|

|

|

1 | TX1PEND | TX1PEND masked interrupt read | |

|

|

|

|

0 | TX0PEND | TX0PEND masked interrupt read | |

|

|

|

|

SPRUFL5B | EMAC/MDIO Module | 91 |

Submit Documentation Feedback |

|

|

© 2011, Texas Instruments Incorporated