EMAC Module Registers | www.ti.com |

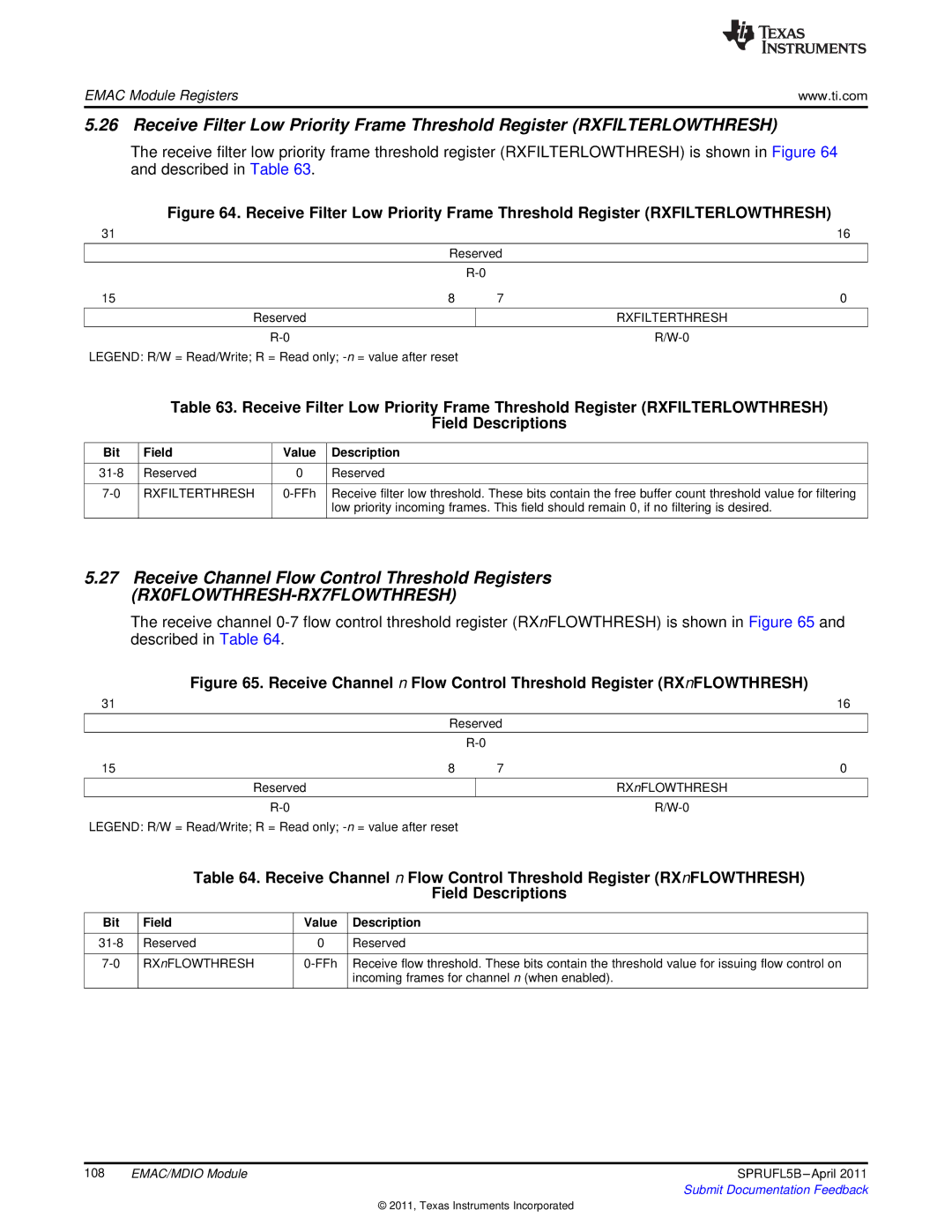

5.26 Receive Filter Low Priority Frame Threshold Register (RXFILTERLOWTHRESH)

The receive filter low priority frame threshold register (RXFILTERLOWTHRESH) is shown in Figure 64 and described in Table 63.

Figure 64. Receive Filter Low Priority Frame Threshold Register (RXFILTERLOWTHRESH)

31 |

|

|

| 16 |

| Reserved |

| ||

|

|

|

| |

|

|

| ||

15 | 8 | 7 | 0 | |

|

|

|

|

|

Reserved |

|

|

| RXFILTERTHRESH |

|

|

|

|

|

|

|

| ||

LEGEND: R/W = Read/Write; R = Read only;

Table 63. Receive Filter Low Priority Frame Threshold Register (RXFILTERLOWTHRESH)

Field Descriptions

Bit | Field | Value | Description |

|

|

|

|

Reserved | 0 | Reserved | |

|

|

|

|

RXFILTERTHRESH | Receive filter low threshold. These bits contain the free buffer count threshold value for filtering | ||

|

|

| low priority incoming frames. This field should remain 0, if no filtering is desired. |

|

|

|

|

5.27Receive Channel Flow Control Threshold Registers

(RX0FLOWTHRESH-RX7FLOWTHRESH)

The receive channel

Figure 65. Receive Channel n Flow Control Threshold Register (RXnFLOWTHRESH)

31 |

|

|

| 16 |

| Reserved |

| ||

|

|

| ||

15 | 8 | 7 | 0 | |

|

|

|

|

|

Reserved |

|

|

| RXnFLOWTHRESH |

|

|

|

|

|

|

|

| ||

LEGEND: R/W = Read/Write; R = Read only;

Table 64. Receive Channel n Flow Control Threshold Register (RXnFLOWTHRESH)

Field Descriptions

Bit | Field | Value | Description |

|

|

|

|

Reserved | 0 | Reserved | |

|

|

|

|

RXnFLOWTHRESH | Receive flow threshold. These bits contain the threshold value for issuing flow control on | ||

|

|

| incoming frames for channel n (when enabled). |

|

|

|

|

108 | EMAC/MDIO Module | SPRUFL5B |

|

| Submit Documentation Feedback |

© 2011, Texas Instruments Incorporated