| www.ti.com |

............................................................................................. 68 |

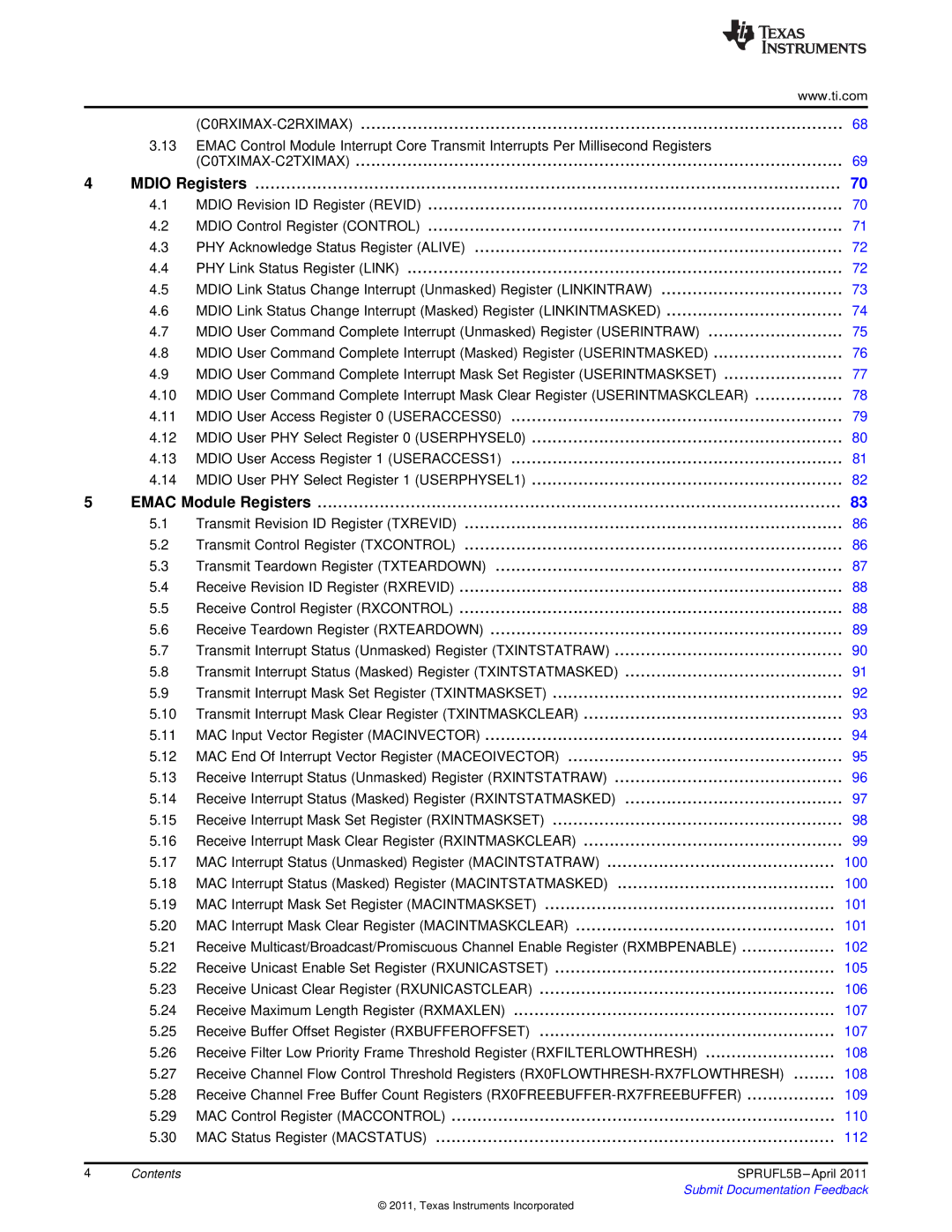

3.13EMAC Control Module Interrupt Core Transmit Interrupts Per Millisecond Registers

|

|

| 69 |

4 | MDIO Registers | 70 | |

| 4.1 | MDIO Revision ID Register (REVID) | 70 |

| 4.2 | MDIO Control Register (CONTROL) | 71 |

| 4.3 | PHY Acknowledge Status Register (ALIVE) | 72 |

| 4.4 | PHY Link Status Register (LINK) | 72 |

| 4.5 | MDIO Link Status Change Interrupt (Unmasked) Register (LINKINTRAW) | 73 |

| 4.6 | MDIO Link Status Change Interrupt (Masked) Register (LINKINTMASKED) | 74 |

| 4.7 | MDIO User Command Complete Interrupt (Unmasked) Register (USERINTRAW) | 75 |

| 4.8 | MDIO User Command Complete Interrupt (Masked) Register (USERINTMASKED) | 76 |

| 4.9 | MDIO User Command Complete Interrupt Mask Set Register (USERINTMASKSET) | 77 |

| 4.10 | MDIO User Command Complete Interrupt Mask Clear Register (USERINTMASKCLEAR) | 78 |

| 4.11 | MDIO User Access Register 0 (USERACCESS0) | 79 |

| 4.12 | MDIO User PHY Select Register 0 (USERPHYSEL0) | 80 |

| 4.13 | MDIO User Access Register 1 (USERACCESS1) | 81 |

| 4.14 | MDIO User PHY Select Register 1 (USERPHYSEL1) | 82 |

5 | EMAC Module Registers | 83 | |

| 5.1 | Transmit Revision ID Register (TXREVID) | 86 |

| 5.2 | Transmit Control Register (TXCONTROL) | 86 |

| 5.3 | Transmit Teardown Register (TXTEARDOWN) | 87 |

| 5.4 | Receive Revision ID Register (RXREVID) | 88 |

| 5.5 | Receive Control Register (RXCONTROL) | 88 |

| 5.6 | Receive Teardown Register (RXTEARDOWN) | 89 |

| 5.7 | Transmit Interrupt Status (Unmasked) Register (TXINTSTATRAW) | 90 |

| 5.8 | Transmit Interrupt Status (Masked) Register (TXINTSTATMASKED) | 91 |

| 5.9 | Transmit Interrupt Mask Set Register (TXINTMASKSET) | 92 |

| 5.10 | Transmit Interrupt Mask Clear Register (TXINTMASKCLEAR) | 93 |

| 5.11 | MAC Input Vector Register (MACINVECTOR) | 94 |

| 5.12 | MAC End Of Interrupt Vector Register (MACEOIVECTOR) | 95 |

| 5.13 | Receive Interrupt Status (Unmasked) Register (RXINTSTATRAW) | 96 |

| 5.14 | Receive Interrupt Status (Masked) Register (RXINTSTATMASKED) | 97 |

| 5.15 | Receive Interrupt Mask Set Register (RXINTMASKSET) | 98 |

| 5.16 | Receive Interrupt Mask Clear Register (RXINTMASKCLEAR) | 99 |

| 5.17 | MAC Interrupt Status (Unmasked) Register (MACINTSTATRAW) | 100 |

| 5.18 | MAC Interrupt Status (Masked) Register (MACINTSTATMASKED) | 100 |

| 5.19 | MAC Interrupt Mask Set Register (MACINTMASKSET) | 101 |

| 5.20 | MAC Interrupt Mask Clear Register (MACINTMASKCLEAR) | 101 |

| 5.21 | Receive Multicast/Broadcast/Promiscuous Channel Enable Register (RXMBPENABLE) | 102 |

| 5.22 | Receive Unicast Enable Set Register (RXUNICASTSET) | 105 |

| 5.23 | Receive Unicast Clear Register (RXUNICASTCLEAR) | 106 |

| 5.24 | Receive Maximum Length Register (RXMAXLEN) | 107 |

| 5.25 | Receive Buffer Offset Register (RXBUFFEROFFSET) | 107 |

| 5.26 | Receive Filter Low Priority Frame Threshold Register (RXFILTERLOWTHRESH) | 108 |

| 5.27 | Receive Channel Flow Control Threshold Registers | 108 |

| 5.28 | Receive Channel Free Buffer Count Registers | 109 |

| 5.29 | MAC Control Register (MACCONTROL) | 110 |

| 5.30 | MAC Status Register (MACSTATUS) | 112 |

|

|

| |

4 | Contents | SPRUFL5B | |

|

| Submit Documentation Feedback | |

© 2011, Texas Instruments Incorporated