EMAC Module Registers | www.ti.com |

5.30 MAC Status Register (MACSTATUS)

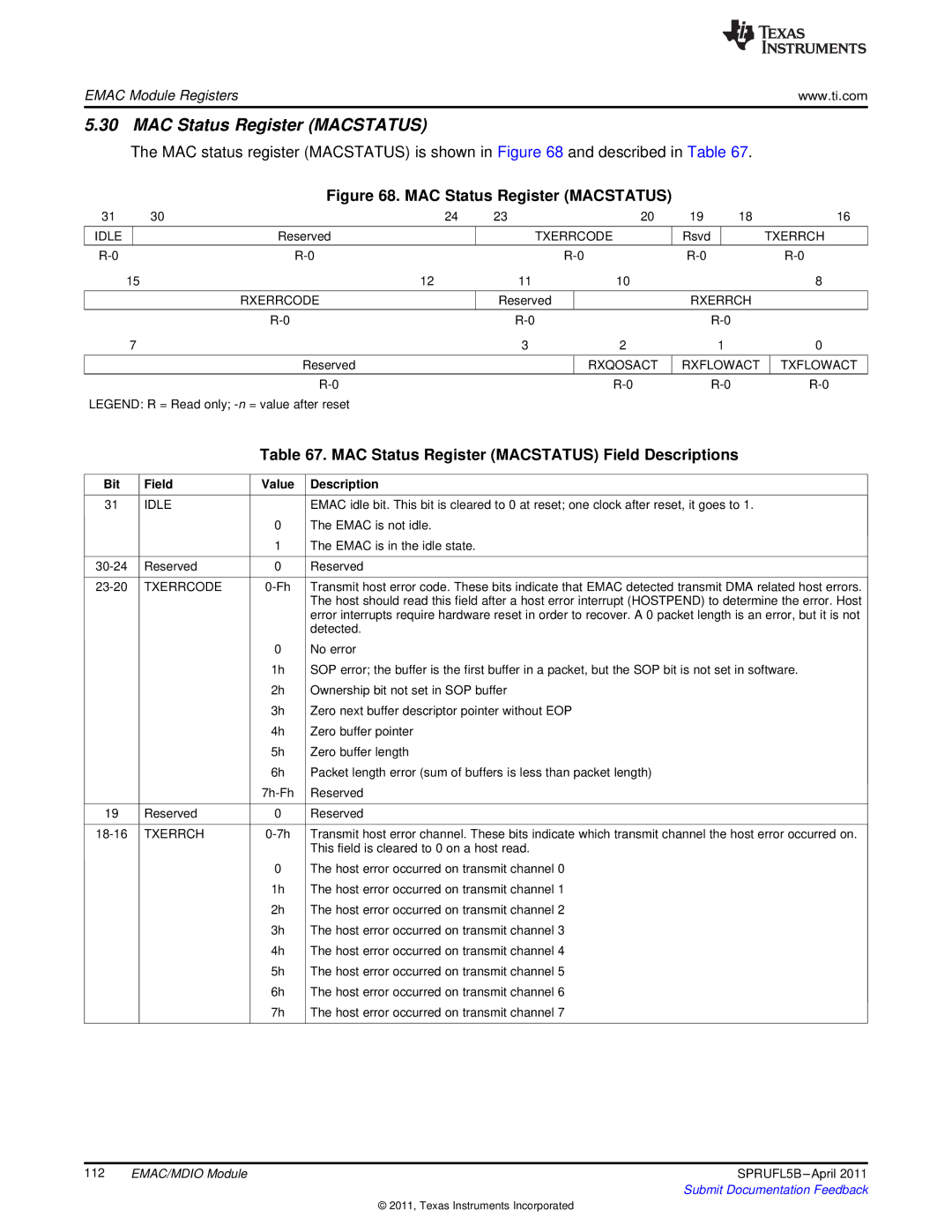

The MAC status register (MACSTATUS) is shown in Figure 68 and described in Table 67.

Figure 68. MAC Status Register (MACSTATUS)

31 | 30 | 24 | 23 | 20 | 19 | 18 | 16 | ||||

IDLE |

| Reserved |

|

| TXERRCODE | Rsvd |

|

| TXERRCH | ||

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

| ||||||

| 15 | 12 | 11 | 10 |

|

|

| 8 | |||

|

|

|

|

|

|

|

|

| |||

|

| RXERRCODE |

| Reserved |

| RXERRCH |

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| 7 |

| 3 | 2 |

| 1 | 0 | ||||

|

|

|

|

|

|

|

|

|

|

| |

|

| Reserved |

|

|

| RXQOSACT | RXFLOWACT |

| TXFLOWACT | ||

|

|

|

|

|

|

| |||||

LEGEND: R = Read only;

Table 67. MAC Status Register (MACSTATUS) Field Descriptions

Bit | Field | Value | Description |

|

|

|

|

31 | IDLE |

| EMAC idle bit. This bit is cleared to 0 at reset; one clock after reset, it goes to 1. |

|

| 0 | The EMAC is not idle. |

|

| 1 | The EMAC is in the idle state. |

|

|

|

|

Reserved | 0 | Reserved | |

|

|

|

|

TXERRCODE | Transmit host error code. These bits indicate that EMAC detected transmit DMA related host errors. | ||

|

|

| The host should read this field after a host error interrupt (HOSTPEND) to determine the error. Host |

|

|

| error interrupts require hardware reset in order to recover. A 0 packet length is an error, but it is not |

|

|

| detected. |

|

| 0 | No error |

|

| 1h | SOP error; the buffer is the first buffer in a packet, but the SOP bit is not set in software. |

|

| 2h | Ownership bit not set in SOP buffer |

|

| 3h | Zero next buffer descriptor pointer without EOP |

|

| 4h | Zero buffer pointer |

|

| 5h | Zero buffer length |

|

| 6h | Packet length error (sum of buffers is less than packet length) |

|

| Reserved | |

|

|

|

|

19 | Reserved | 0 | Reserved |

|

|

|

|

TXERRCH | Transmit host error channel. These bits indicate which transmit channel the host error occurred on. | ||

|

|

| This field is cleared to 0 on a host read. |

|

| 0 | The host error occurred on transmit channel 0 |

|

| 1h | The host error occurred on transmit channel 1 |

|

| 2h | The host error occurred on transmit channel 2 |

|

| 3h | The host error occurred on transmit channel 3 |

|

| 4h | The host error occurred on transmit channel 4 |

|

| 5h | The host error occurred on transmit channel 5 |

|

| 6h | The host error occurred on transmit channel 6 |

|

| 7h | The host error occurred on transmit channel 7 |

|

|

|

|

112 | EMAC/MDIO Module | SPRUFL5B |

|

| Submit Documentation Feedback |

© 2011, Texas Instruments Incorporated