EMAC Module Registers | www.ti.com |

5.15 Receive Interrupt Mask Set Register (RXINTMASKSET)

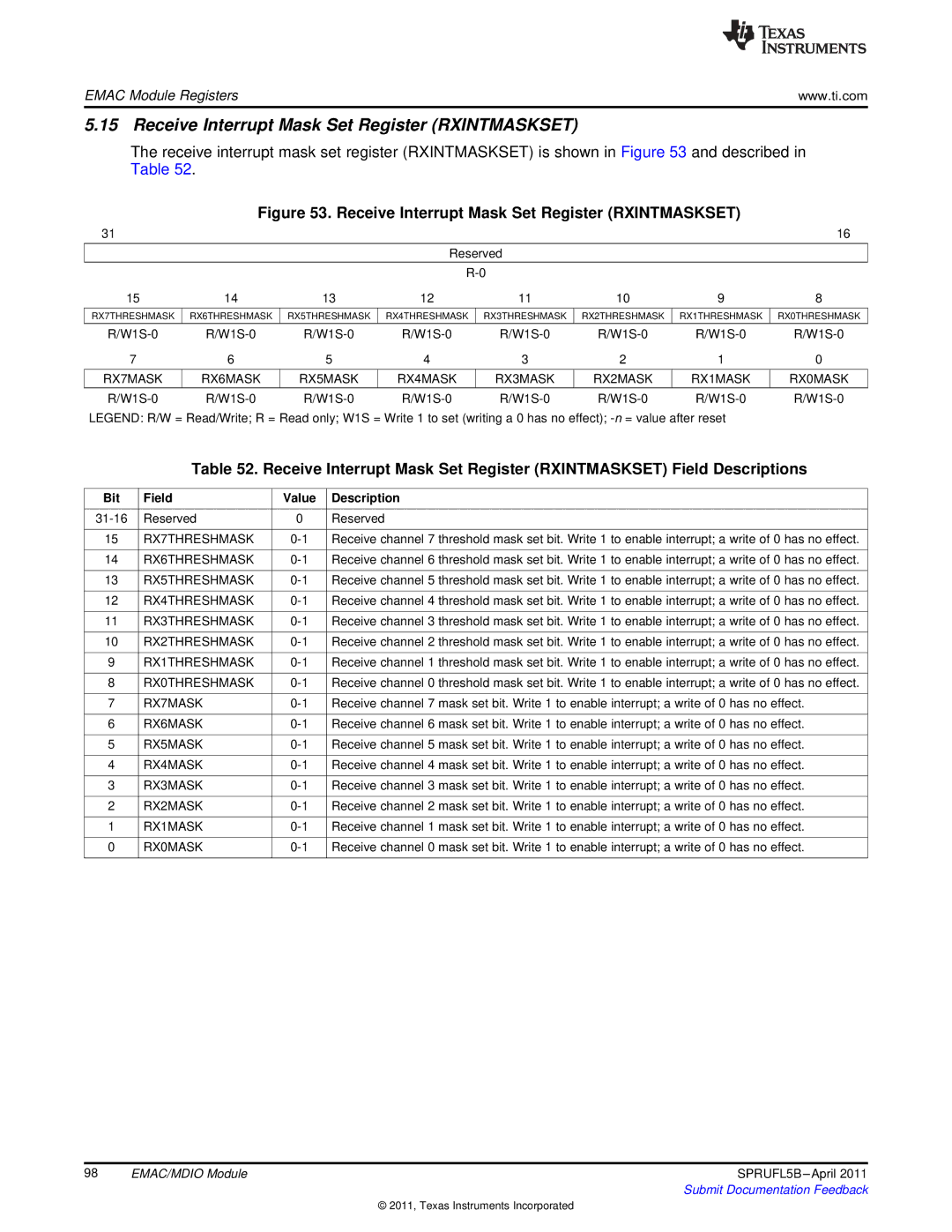

The receive interrupt mask set register (RXINTMASKSET) is shown in Figure 53 and described in Table 52.

Figure 53. Receive Interrupt Mask Set Register (RXINTMASKSET)

31 |

|

|

|

|

|

| 16 |

|

|

| Reserved |

|

|

| |

|

|

|

|

|

|

| |

|

|

|

|

|

| ||

15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

|

|

|

|

|

|

|

|

RX7THRESHMASK | RX6THRESHMASK | RX5THRESHMASK | RX4THRESHMASK | RX3THRESHMASK | RX2THRESHMASK | RX1THRESHMASK | RX0THRESHMASK |

|

|

|

|

|

|

|

|

| |||||||

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|

|

|

|

|

|

|

|

RX7MASK | RX6MASK | RX5MASK | RX4MASK | RX3MASK | RX2MASK | RX1MASK | RX0MASK |

| |||||||

LEGEND: R/W = Read/Write; R = Read only; W1S = Write 1 to set (writing a 0 has no effect);

Table 52. Receive Interrupt Mask Set Register (RXINTMASKSET) Field Descriptions

Bit | Field | Value | Description |

|

|

|

|

Reserved | 0 | Reserved | |

|

|

|

|

15 | RX7THRESHMASK | Receive channel 7 threshold mask set bit. Write 1 to enable interrupt; a write of 0 has no effect. | |

|

|

|

|

14 | RX6THRESHMASK | Receive channel 6 threshold mask set bit. Write 1 to enable interrupt; a write of 0 has no effect. | |

|

|

|

|

13 | RX5THRESHMASK | Receive channel 5 threshold mask set bit. Write 1 to enable interrupt; a write of 0 has no effect. | |

|

|

|

|

12 | RX4THRESHMASK | Receive channel 4 threshold mask set bit. Write 1 to enable interrupt; a write of 0 has no effect. | |

|

|

|

|

11 | RX3THRESHMASK | Receive channel 3 threshold mask set bit. Write 1 to enable interrupt; a write of 0 has no effect. | |

|

|

|

|

10 | RX2THRESHMASK | Receive channel 2 threshold mask set bit. Write 1 to enable interrupt; a write of 0 has no effect. | |

|

|

|

|

9 | RX1THRESHMASK | Receive channel 1 threshold mask set bit. Write 1 to enable interrupt; a write of 0 has no effect. | |

|

|

|

|

8 | RX0THRESHMASK | Receive channel 0 threshold mask set bit. Write 1 to enable interrupt; a write of 0 has no effect. | |

|

|

|

|

7 | RX7MASK | Receive channel 7 mask set bit. Write 1 to enable interrupt; a write of 0 has no effect. | |

|

|

|

|

6 | RX6MASK | Receive channel 6 mask set bit. Write 1 to enable interrupt; a write of 0 has no effect. | |

|

|

|

|

5 | RX5MASK | Receive channel 5 mask set bit. Write 1 to enable interrupt; a write of 0 has no effect. | |

|

|

|

|

4 | RX4MASK | Receive channel 4 mask set bit. Write 1 to enable interrupt; a write of 0 has no effect. | |

|

|

|

|

3 | RX3MASK | Receive channel 3 mask set bit. Write 1 to enable interrupt; a write of 0 has no effect. | |

|

|

|

|

2 | RX2MASK | Receive channel 2 mask set bit. Write 1 to enable interrupt; a write of 0 has no effect. | |

|

|

|

|

1 | RX1MASK | Receive channel 1 mask set bit. Write 1 to enable interrupt; a write of 0 has no effect. | |

|

|

|

|

0 | RX0MASK | Receive channel 0 mask set bit. Write 1 to enable interrupt; a write of 0 has no effect. | |

|

|

|

|

98 | EMAC/MDIO Module | SPRUFL5B |

|

| Submit Documentation Feedback |

© 2011, Texas Instruments Incorporated