www.ti.com | EMAC Module Registers |

5.28 Receive Channel Free Buffer Count Registers

The receive channel

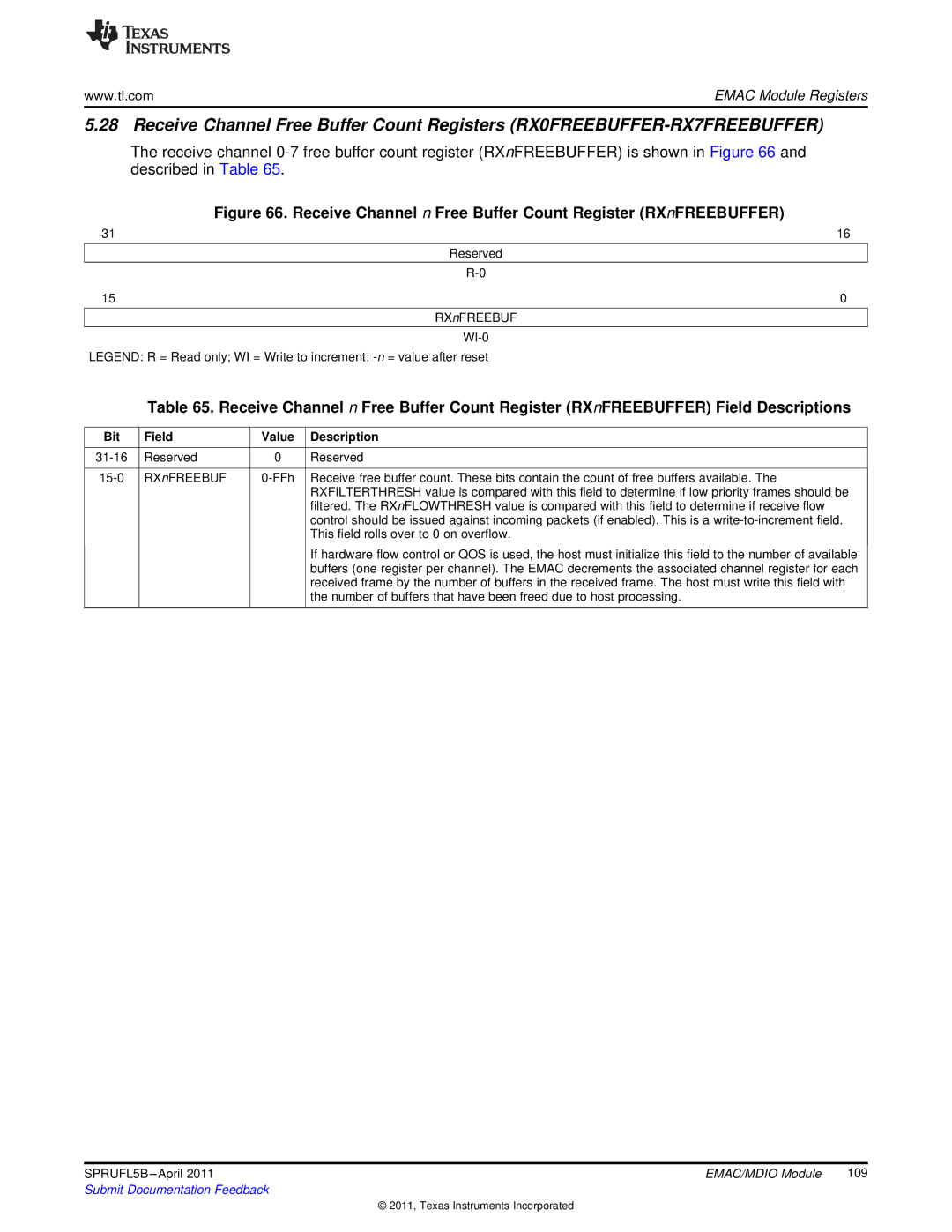

| Figure 66. Receive Channel n Free Buffer Count Register (RXnFREEBUFFER) | ||

31 |

|

| 16 |

|

|

|

|

|

|

| Reserved |

|

|

|

|

|

|

| |

15 |

|

| 0 |

|

|

|

|

|

|

| RXnFREEBUF |

|

|

|

|

|

|

| |

LEGEND: R = Read only; WI = Write to increment; | |||

| Table 65. Receive Channel n Free Buffer Count Register (RXnFREEBUFFER) Field Descriptions | ||

|

|

|

|

Bit | Field | Value | Description |

|

|

|

|

Reserved | 0 | Reserved | |

|

|

|

|

RXnFREEBUF | Receive free buffer count. These bits contain the count of free buffers available. The | ||

|

|

| RXFILTERTHRESH value is compared with this field to determine if low priority frames should be |

|

|

| filtered. The RXnFLOWTHRESH value is compared with this field to determine if receive flow |

|

|

| control should be issued against incoming packets (if enabled). This is a |

|

|

| This field rolls over to 0 on overflow. |

|

|

| If hardware flow control or QOS is used, the host must initialize this field to the number of available |

|

|

| buffers (one register per channel). The EMAC decrements the associated channel register for each |

|

|

| received frame by the number of buffers in the received frame. The host must write this field with |

|

|

| the number of buffers that have been freed due to host processing. |

|

|

|

|

SPRUFL5B | EMAC/MDIO Module | 109 |

Submit Documentation Feedback |

|

|

© 2011, Texas Instruments Incorporated