MDIO Registers | www.ti.com |

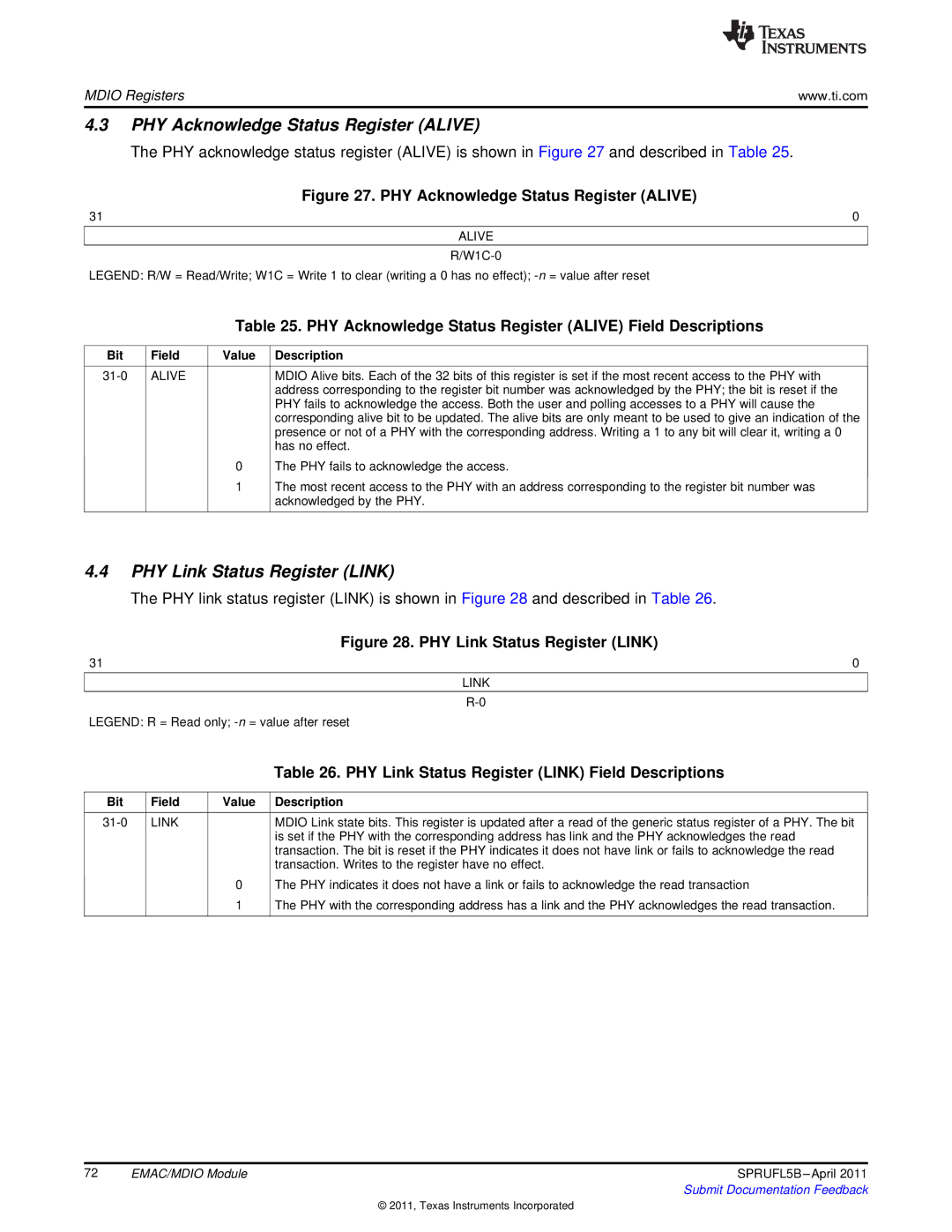

4.3PHY Acknowledge Status Register (ALIVE)

The PHY acknowledge status register (ALIVE) is shown in Figure 27 and described in Table 25.

Figure 27. PHY Acknowledge Status Register (ALIVE)

31 | 0 |

ALIVE

LEGEND: R/W = Read/Write; W1C = Write 1 to clear (writing a 0 has no effect);

Table 25. PHY Acknowledge Status Register (ALIVE) Field Descriptions

Bit | Field | Value | Description |

|

|

|

|

ALIVE |

| MDIO Alive bits. Each of the 32 bits of this register is set if the most recent access to the PHY with | |

|

|

| address corresponding to the register bit number was acknowledged by the PHY; the bit is reset if the |

|

|

| PHY fails to acknowledge the access. Both the user and polling accesses to a PHY will cause the |

|

|

| corresponding alive bit to be updated. The alive bits are only meant to be used to give an indication of the |

|

|

| presence or not of a PHY with the corresponding address. Writing a 1 to any bit will clear it, writing a 0 |

|

|

| has no effect. |

|

| 0 | The PHY fails to acknowledge the access. |

|

| 1 | The most recent access to the PHY with an address corresponding to the register bit number was |

|

|

| acknowledged by the PHY. |

|

|

|

|

4.4PHY Link Status Register (LINK)

The PHY link status register (LINK) is shown in Figure 28 and described in Table 26.

Figure 28. PHY Link Status Register (LINK)

31 | 0 |

LINK

LEGEND: R = Read only;

|

|

| Table 26. PHY Link Status Register (LINK) Field Descriptions |

|

|

|

|

Bit | Field | Value | Description |

|

|

|

|

LINK |

| MDIO Link state bits. This register is updated after a read of the generic status register of a PHY. The bit | |

|

|

| is set if the PHY with the corresponding address has link and the PHY acknowledges the read |

|

|

| transaction. The bit is reset if the PHY indicates it does not have link or fails to acknowledge the read |

|

|

| transaction. Writes to the register have no effect. |

|

| 0 | The PHY indicates it does not have a link or fails to acknowledge the read transaction |

|

| 1 | The PHY with the corresponding address has a link and the PHY acknowledges the read transaction. |

|

|

|

|

72 | EMAC/MDIO Module | SPRUFL5B |

|

| Submit Documentation Feedback |

© 2011, Texas Instruments Incorporated