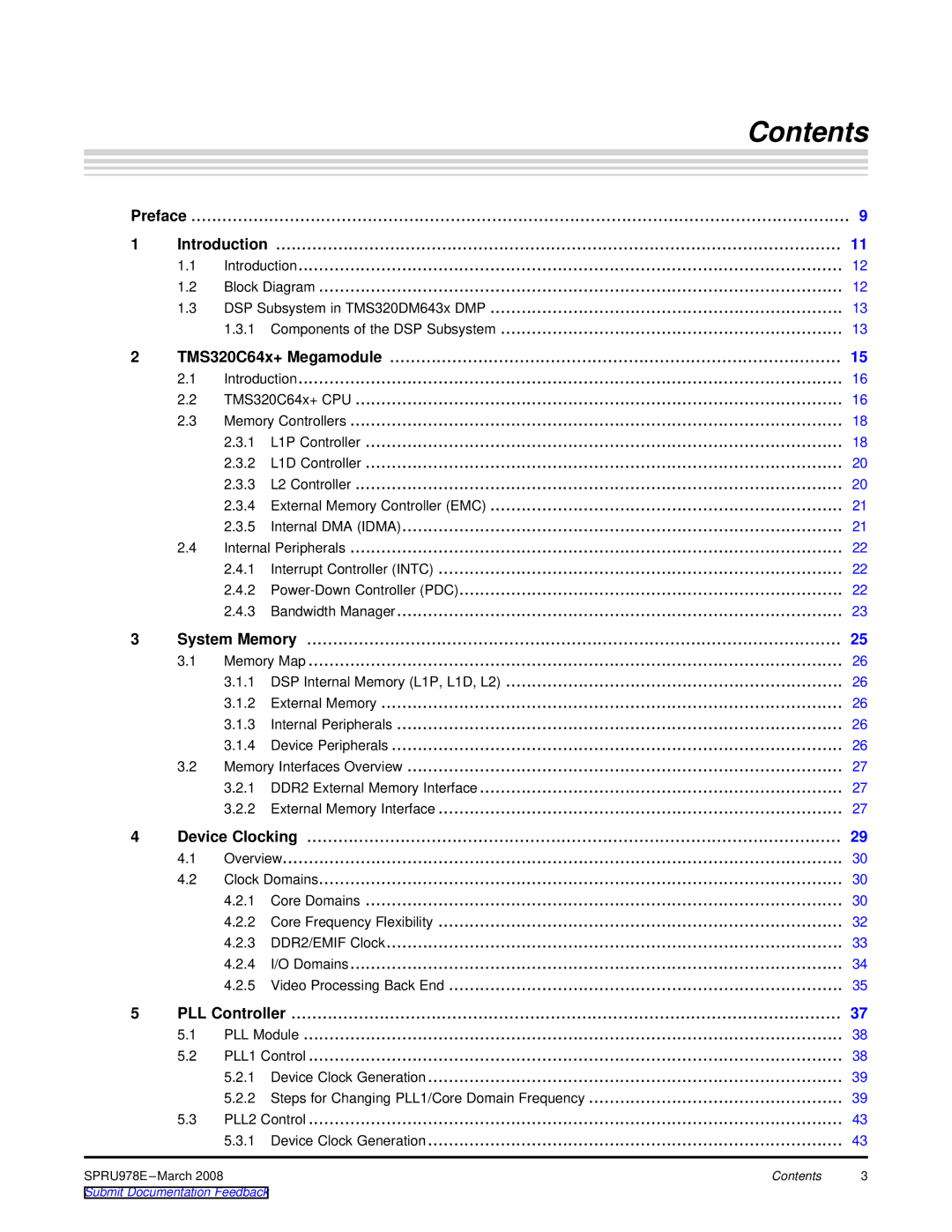

Contents

Preface | 9 | ||

1 | Introduction | 11 | |

| 1.1 | Introduction | 12 |

| 1.2 | Block Diagram | 12 |

| 1.3 | DSP Subsystem in TMS320DM643x DMP | 13 |

|

| 1.3.1 Components of the DSP Subsystem | 13 |

2 | TMS320C64x+ Megamodule | 15 | ||

| 2.1 | Introduction | 16 | |

| 2.2 | TMS320C64x+ CPU | 16 | |

| 2.3 | Memory Controllers | 18 | |

|

| 2.3.1 | L1P Controller | 18 |

|

| 2.3.2 | L1D Controller | 20 |

|

| 2.3.3 | L2 Controller | 20 |

|

| 2.3.4 External Memory Controller (EMC) | 21 | |

|

| 2.3.5 | Internal DMA (IDMA) | 21 |

| 2.4 | Internal Peripherals | 22 | |

|

| 2.4.1 | Interrupt Controller (INTC) | 22 |

|

| 2.4.2 | 22 | |

|

| 2.4.3 | Bandwidth Manager | 23 |

3 | System Memory | 25 | ||

| 3.1 | Memory Map | 26 | |

|

| 3.1.1 DSP Internal Memory (L1P, L1D, L2) | 26 | |

|

| 3.1.2 | External Memory | 26 |

|

| 3.1.3 | Internal Peripherals | 26 |

|

| 3.1.4 | Device Peripherals | 26 |

| 3.2 | Memory Interfaces Overview | 27 | |

|

| 3.2.1 DDR2 External Memory Interface | 27 | |

|

| 3.2.2 | External Memory Interface | 27 |

4 | Device Clocking | 29 | ||

| 4.1 | Overview | 30 | |

| 4.2 | Clock Domains | 30 | |

|

| 4.2.1 | Core Domains | 30 |

|

| 4.2.2 | Core Frequency Flexibility | 32 |

|

| 4.2.3 | DDR2/EMIF Clock | 33 |

|

| 4.2.4 | I/O Domains | 34 |

|

| 4.2.5 Video Processing Back End | 35 | |

5 | PLL Controller | 37 | ||

| 5.1 | PLL Module | 38 | |

| 5.2 | PLL1 Control | 38 | |

|

| 5.2.1 | Device Clock Generation | 39 |

|

| 5.2.2 Steps for Changing PLL1/Core Domain Frequency | 39 | |

| 5.3 | PLL2 Control | 43 | |

|

| 5.3.1 | Device Clock Generation | 43 |

| Contents | 3 | ||