www.ti.com

PSC Registers

6.6.3 Interrupt Handling

Handle the PSC interrupts as described in the following procedure:

First, enable the interrupt.

1.Set the EMUIHBIE bit and the EMURSTIE bit in MDCTL39 to enable the interrupt events that you want.

Note: The PSC interrupt PSCINT is sent to the DSP interrupt controller when at least one enabled event becomes active.

2.Enable the power and sleep controller interrupt (PSCINT) in the DSP interrupt controller. To interrupt the DSP, PSCINT must be enabled in the DSP interrupt controller. See Section 2.4.1 for more information.

The DSP enters the interrupt service routine (ISR) when it receives the interrupt.

1.Read the Mn bit in MERRPR1 to determine the source of the interrupt(s). Note that on the DM643x DMP, only M[39] can cause an interrupt.

2.For each active event that you want to service:

∙Read the event status bits in MDSTAT39, depending on the status bits read in the previous step to determine the event that caused the interrupt.

∙Service the interrupt as required by your application.

∙Write the M[39] bit in MERRCR1 to clear corresponding status.

∙Set the ALLEV bit in INTEVAL to 1. Setting this bit reasserts the PSCINT to the DSP interrupt controller, if there are still any active interrupt events.

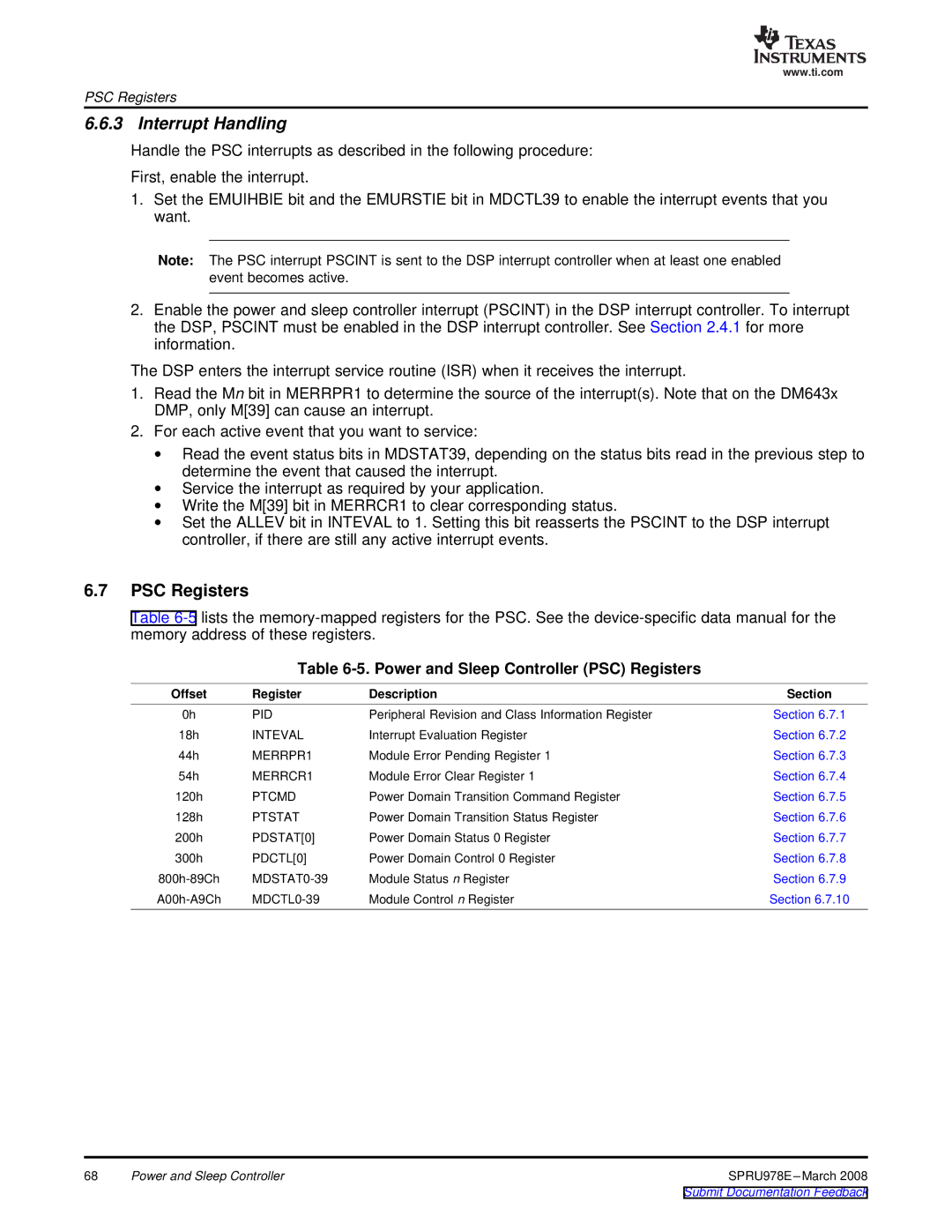

6.7PSC Registers

Table

Table 6-5. Power and Sleep Controller (PSC) Registers

Offset | Register | Description | Section |

0h | PID | Peripheral Revision and Class Information Register | Section 6.7.1 |

18h | INTEVAL | Interrupt Evaluation Register | Section 6.7.2 |

44h | MERRPR1 | Module Error Pending Register 1 | Section 6.7.3 |

54h | MERRCR1 | Module Error Clear Register 1 | Section 6.7.4 |

120h | PTCMD | Power Domain Transition Command Register | Section 6.7.5 |

128h | PTSTAT | Power Domain Transition Status Register | Section 6.7.6 |

200h | PDSTAT[0] | Power Domain Status 0 Register | Section 6.7.7 |

300h | PDCTL[0] | Power Domain Control 0 Register | Section 6.7.8 |

Module Status n Register | Section 6.7.9 | ||

Module Control n Register | Section 6.7.10 |

68 | Power and Sleep Controller | |

|

| Submit Documentation Feedback |