www.ti.com

Bandwidth Management

9.6Bandwidth Management

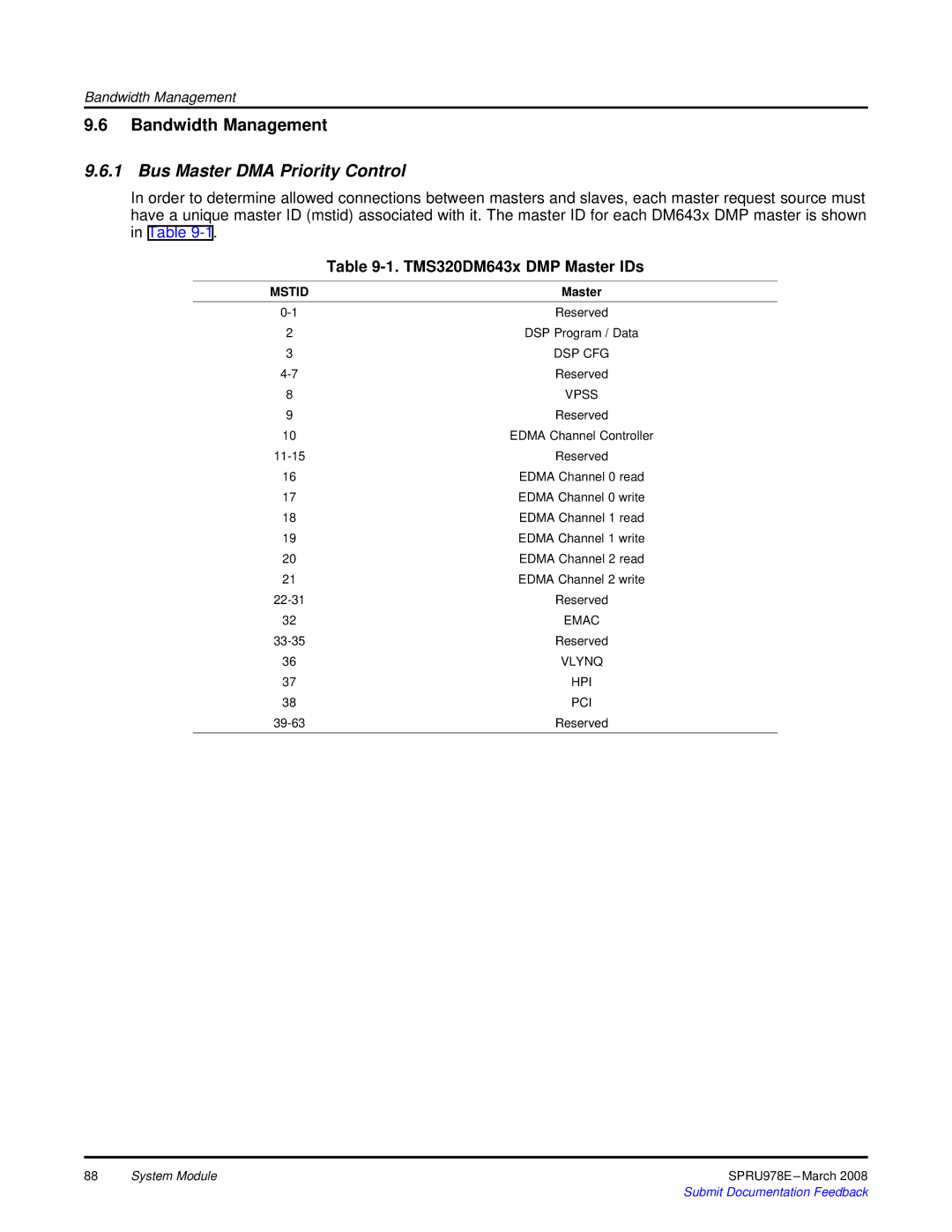

9.6.1 Bus Master DMA Priority Control

In order to determine allowed connections between masters and slaves, each master request source must have a unique master ID (mstid) associated with it. The master ID for each DM643x DMP master is shown in Table

| Table |

MSTID | Master |

Reserved | |

2 | DSP Program / Data |

3 | DSP CFG |

Reserved | |

8 | VPSS |

9 | Reserved |

10 | EDMA Channel Controller |

Reserved | |

16 | EDMA Channel 0 read |

17 | EDMA Channel 0 write |

18 | EDMA Channel 1 read |

19 | EDMA Channel 1 write |

20 | EDMA Channel 2 read |

21 | EDMA Channel 2 write |

Reserved | |

32 | EMAC |

Reserved | |

36 | VLYNQ |

37 | HPI |

38 | PCI |

Reserved |

88 | System Module |