www.ti.com

Overview

4.1Overview

The DM643x DMP requires one primary reference clock. The primary reference clock can be either crystal input or driven by external oscillators. A 27 MHZ crystal at the MXI/CLKIN pin is recommended for the system PLLs, which generate the clocks for the DSP, peripherals, DMA, and imaging peripherals. The recommended 27 MHZ input enables you to use the video DACs to drive NTSC/PAL television signals at the proper frequencies.

For detailed specifications on clock frequency and voltage requirements, see the

There are two clocking modes:

∙PLL Bypass Mode - power saving (device defaults to this mode)

∙PLL Mode - PLL multiplies input clock up to the desired operating frequency

The clock of the major chip subsystems must be programmed to operate at fixed ratios of the primary system/DSP clock frequency within each mode, as shown in Table

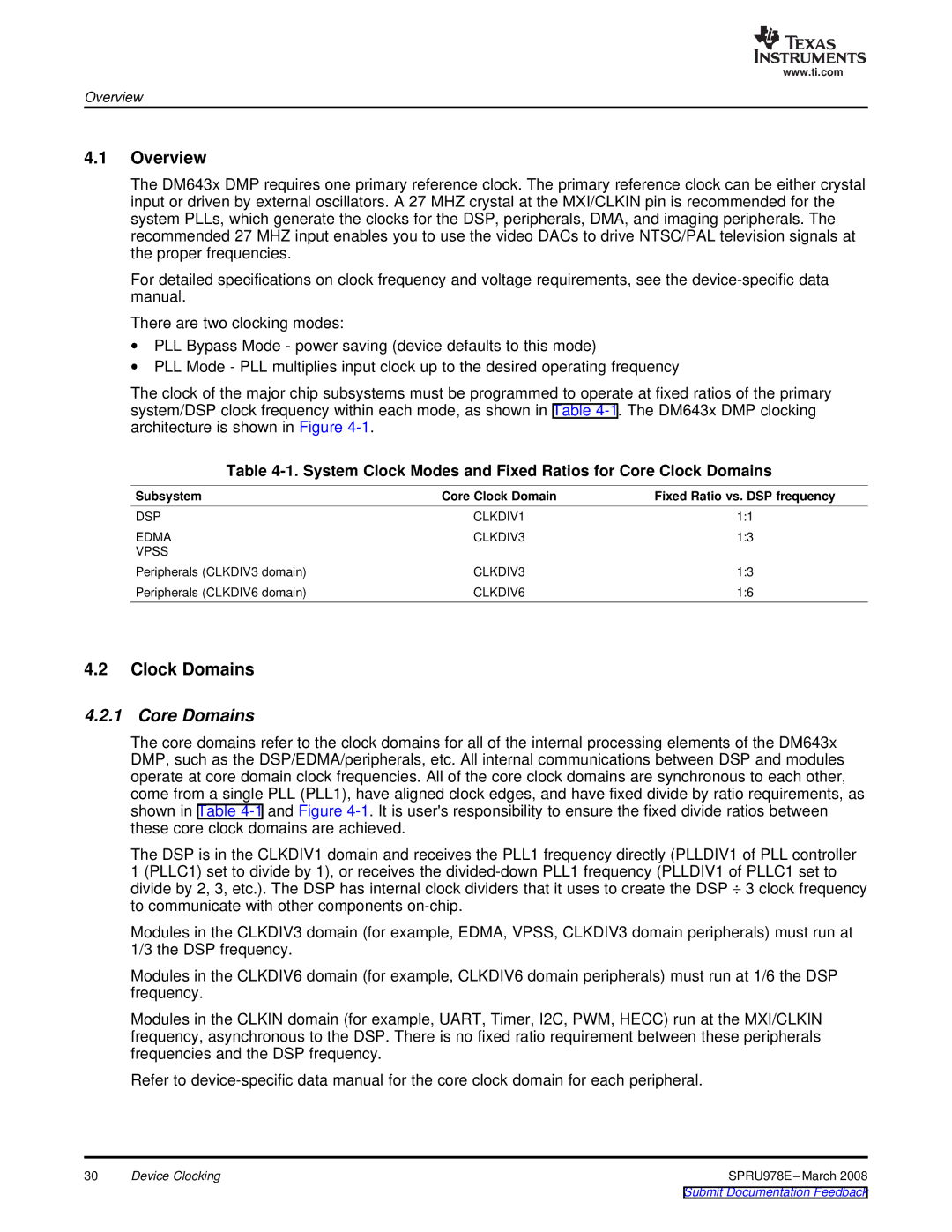

Table 4-1. System Clock Modes and Fixed Ratios for Core Clock Domains

Subsystem | Core Clock Domain | Fixed Ratio vs. DSP frequency |

DSP | CLKDIV1 | 1:1 |

EDMA | CLKDIV3 | 1:3 |

VPSS |

|

|

Peripherals (CLKDIV3 domain) | CLKDIV3 | 1:3 |

Peripherals (CLKDIV6 domain) | CLKDIV6 | 1:6 |

4.2Clock Domains

4.2.1 Core Domains

The core domains refer to the clock domains for all of the internal processing elements of the DM643x DMP, such as the DSP/EDMA/peripherals, etc. All internal communications between DSP and modules operate at core domain clock frequencies. All of the core clock domains are synchronous to each other, come from a single PLL (PLL1), have aligned clock edges, and have fixed divide by ratio requirements, as shown in Table

The DSP is in the CLKDIV1 domain and receives the PLL1 frequency directly (PLLDIV1 of PLL controller 1 (PLLC1) set to divide by 1), or receives the

Modules in the CLKDIV3 domain (for example, EDMA, VPSS, CLKDIV3 domain peripherals) must run at 1/3 the DSP frequency.

Modules in the CLKDIV6 domain (for example, CLKDIV6 domain peripherals) must run at 1/6 the DSP frequency.

Modules in the CLKIN domain (for example, UART, Timer, I2C, PWM, HECC) run at the MXI/CLKIN frequency, asynchronous to the DSP. There is no fixed ratio requirement between these peripherals frequencies and the DSP frequency.

Refer to

30 | Device Clocking |