www.ti.com

PSC Registers

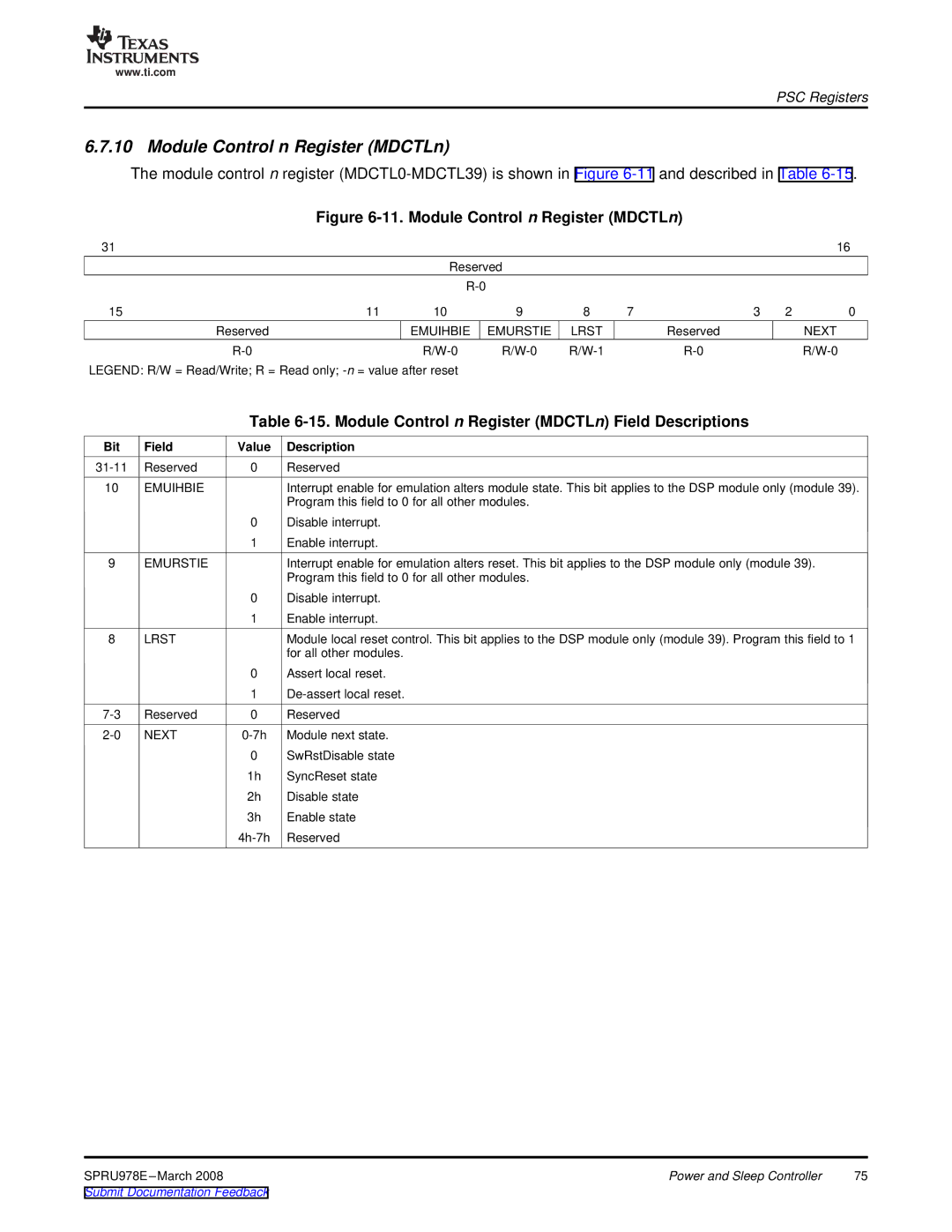

6.7.10 Module Control n Register (MDCTLn)

The module control n register

Figure 6-11. Module Control n Register (MDCTLn)

31 |

|

|

|

|

|

|

| 16 |

|

| Reserved |

|

|

|

|

| |

|

|

|

|

|

|

|

| |

15 | 11 | 10 | 9 | 8 | 7 | 3 | 2 | 0 |

Reserved |

| EMUIHBIE | EMURSTIE | LRST | Reserved |

|

| NEXT |

|

|

| ||||||

LEGEND: R/W = Read/Write; R = Read only;

Table 6-15. Module Control n Register (MDCTLn) Field Descriptions

Bit | Field | Value | Description |

Reserved | 0 | Reserved | |

10 | EMUIHBIE |

| Interrupt enable for emulation alters module state. This bit applies to the DSP module only (module 39). |

|

|

| Program this field to 0 for all other modules. |

|

| 0 | Disable interrupt. |

|

| 1 | Enable interrupt. |

9 | EMURSTIE |

| Interrupt enable for emulation alters reset. This bit applies to the DSP module only (module 39). |

|

|

| Program this field to 0 for all other modules. |

|

| 0 | Disable interrupt. |

|

| 1 | Enable interrupt. |

8 | LRST |

| Module local reset control. This bit applies to the DSP module only (module 39). Program this field to 1 |

|

|

| for all other modules. |

|

| 0 | Assert local reset. |

|

| 1 | |

Reserved | 0 | Reserved | |

NEXT | Module next state. | ||

|

| 0 | SwRstDisable state |

|

| 1h | SyncReset state |

|

| 2h | Disable state |

|

| 3h | Enable state |

|

| Reserved |

Power and Sleep Controller | 75 | |

Submit Documentation Feedback |

|

|