www.ti.com

Overview

7.1Overview

In many applications, there may be specific requirements to minimize power consumption for both power supply (or battery) and thermal considerations. There are two components to power consumption: active power and leakage power. Active power is the power consumed to perform work and scales roughly with clock frequency and the amount of computations being performed. Active power can be reduced by controlling the clocks in such a way as to either operate at a clock setting just high enough to complete the required operation in the required timeline or to run at a clock setting until the work is complete and then drastically cut the clocks (that is, to PLL Bypass mode) until additional work must be performed. Leakage power is due to static current leakage and occurs regardless of the clock rate. Leakage, or standby power, is unavoidable while power is applied and scales roughly with the operating junction temperatures. Leakage power can only be avoided by removing power completely from a device or subsystem.

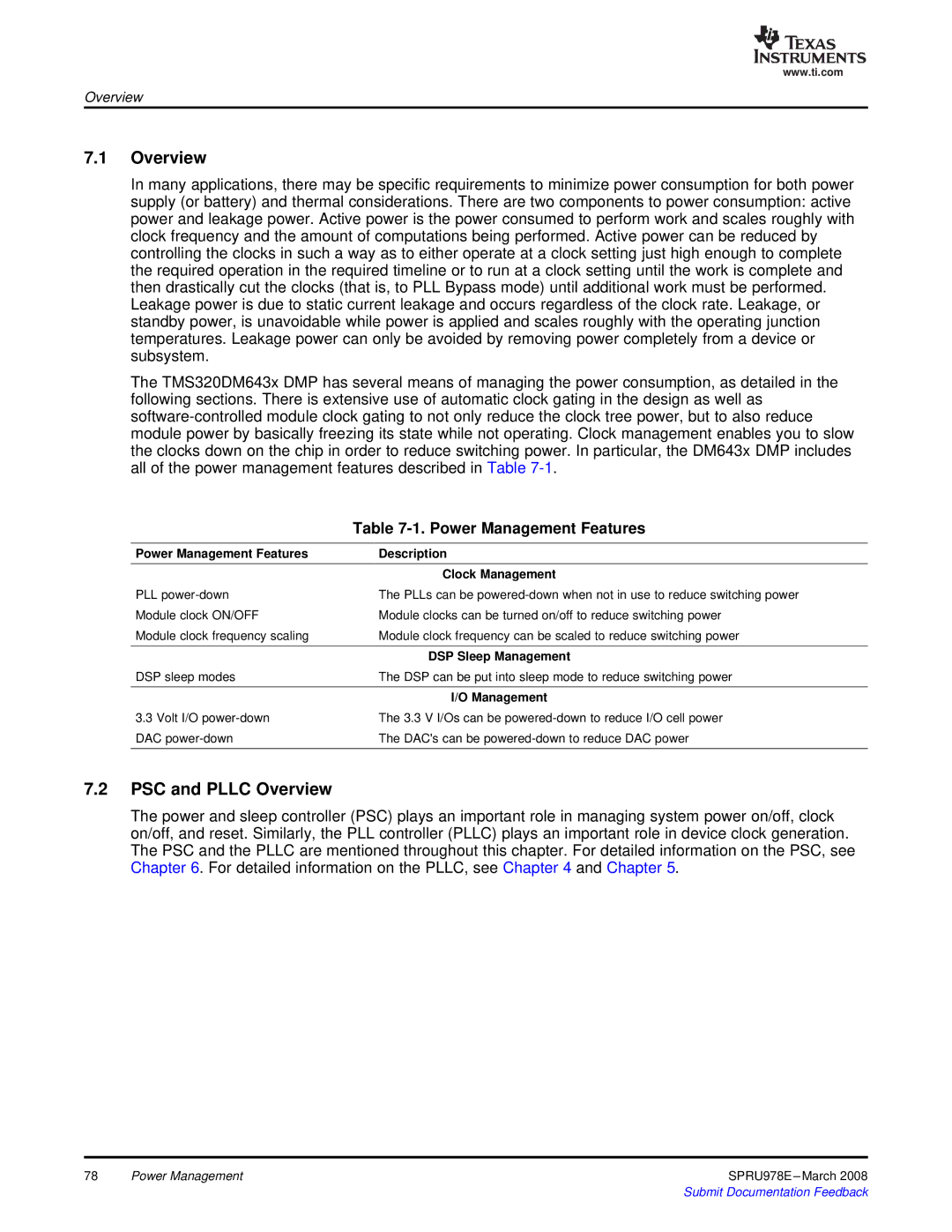

The TMS320DM643x DMP has several means of managing the power consumption, as detailed in the following sections. There is extensive use of automatic clock gating in the design as well as

| Table |

Power Management Features | Description |

| Clock Management |

PLL | The PLLs can be |

Module clock ON/OFF | Module clocks can be turned on/off to reduce switching power |

Module clock frequency scaling | Module clock frequency can be scaled to reduce switching power |

| DSP Sleep Management |

DSP sleep modes | The DSP can be put into sleep mode to reduce switching power |

| I/O Management |

3.3 Volt I/O | The 3.3 V I/Os can be |

DAC | The DAC's can be |

7.2PSC and PLLC Overview

The power and sleep controller (PSC) plays an important role in managing system power on/off, clock on/off, and reset. Similarly, the PLL controller (PLLC) plays an important role in device clock generation. The PSC and the PLLC are mentioned throughout this chapter. For detailed information on the PSC, see Chapter 6. For detailed information on the PLLC, see Chapter 4 and Chapter 5.

78 | Power Management |