www.ti.com

PLL Controller Registers

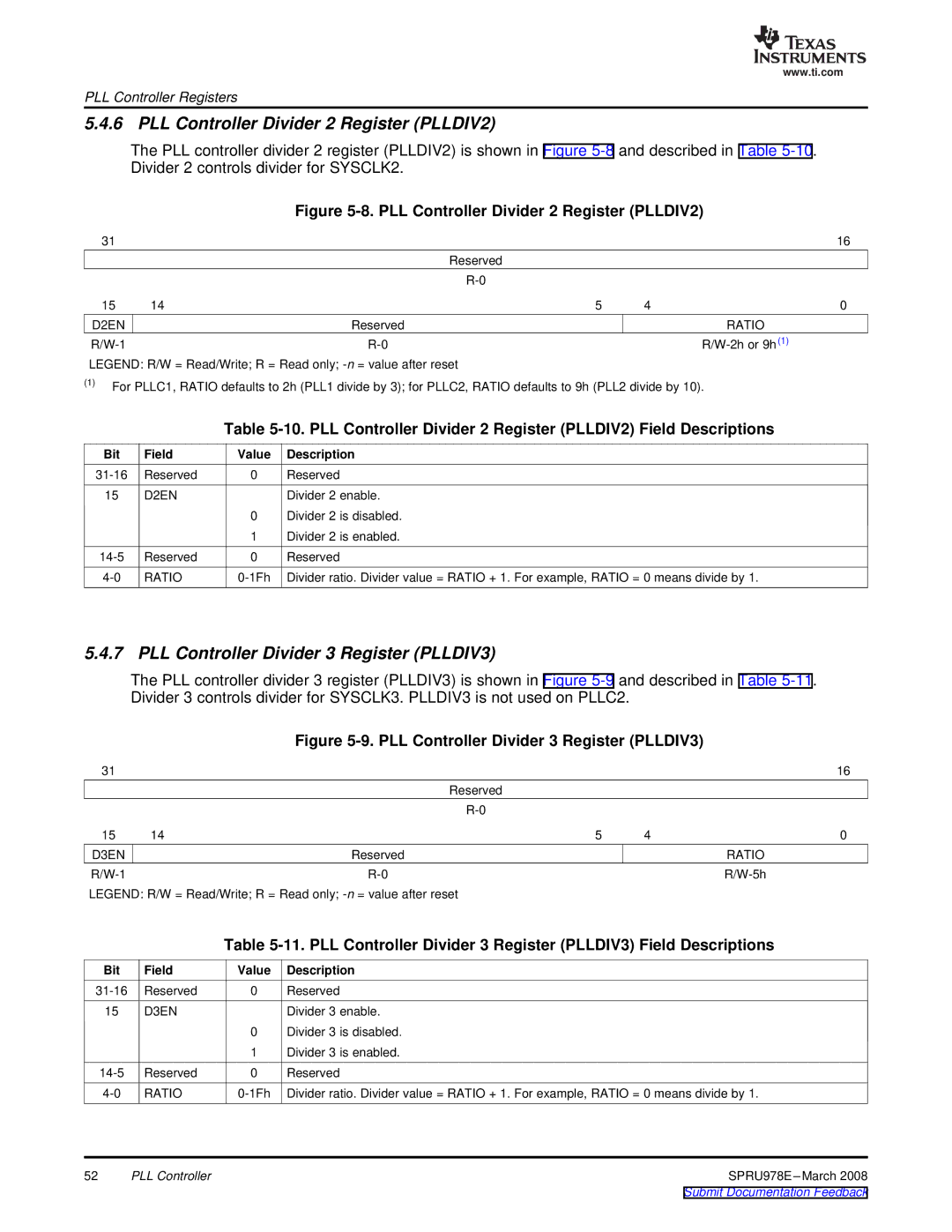

5.4.6 PLL Controller Divider 2 Register (PLLDIV2)

The PLL controller divider 2 register (PLLDIV2) is shown in Figure

Figure 5-8. PLL Controller Divider 2 Register (PLLDIV2)

31 |

|

|

| 16 |

|

| Reserved |

|

|

|

|

|

| |

15 | 14 | 5 | 4 | 0 |

D2EN | Reserved |

|

| RATIO |

|

|

LEGEND: R/W = Read/Write; R = Read only;

(1)For PLLC1, RATIO defaults to 2h (PLL1 divide by 3); for PLLC2, RATIO defaults to 9h (PLL2 divide by 10).

Table

Bit | Field | Value | Description |

Reserved | 0 | Reserved | |

15 | D2EN |

| Divider 2 enable. |

|

| 0 | Divider 2 is disabled. |

|

| 1 | Divider 2 is enabled. |

Reserved | 0 | Reserved | |

RATIO | Divider ratio. Divider value = RATIO + 1. For example, RATIO = 0 means divide by 1. |

5.4.7 PLL Controller Divider 3 Register (PLLDIV3)

The PLL controller divider 3 register (PLLDIV3) is shown in Figure

Figure 5-9. PLL Controller Divider 3 Register (PLLDIV3)

31 |

|

|

| 16 |

|

| Reserved |

|

|

|

|

|

| |

15 | 14 | 5 | 4 | 0 |

D3EN | Reserved |

|

| RATIO |

|

|

LEGEND: R/W = Read/Write; R = Read only;

Table

Bit | Field | Value | Description |

Reserved | 0 | Reserved | |

15 | D3EN |

| Divider 3 enable. |

|

| 0 | Divider 3 is disabled. |

|

| 1 | Divider 3 is enabled. |

Reserved | 0 | Reserved | |

RATIO | Divider ratio. Divider value = RATIO + 1. For example, RATIO = 0 means divide by 1. |

52 | PLL Controller | |

|

| Submit Documentation Feedback |