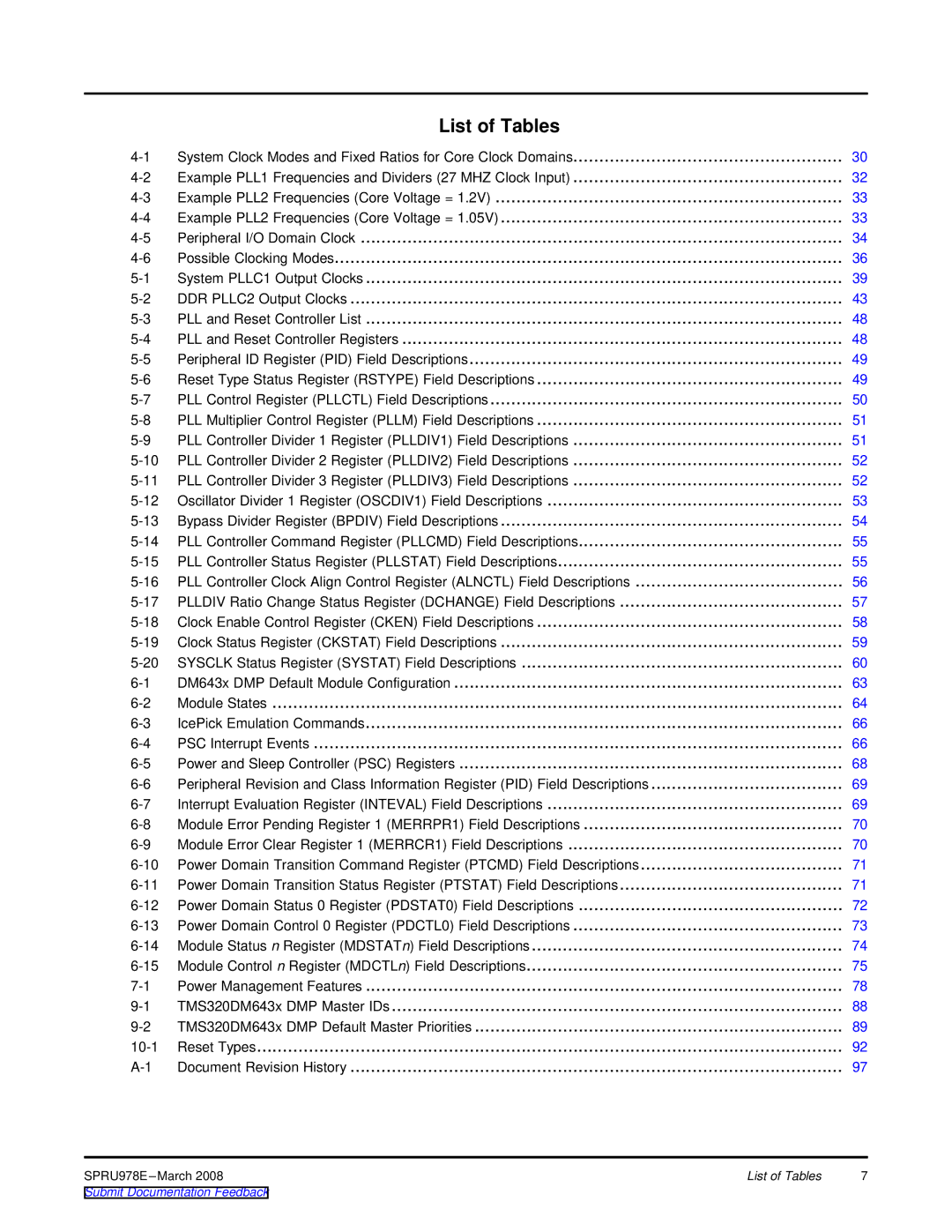

List of Tables

System Clock Modes and Fixed Ratios for Core Clock Domains | 30 | |

Example PLL1 Frequencies and Dividers (27 MHZ Clock Input) | 32 | |

Example PLL2 Frequencies (Core Voltage = 1.2V) | 33 | |

Example PLL2 Frequencies (Core Voltage = 1.05V) | 33 | |

Peripheral I/O Domain Clock | 34 | |

Possible Clocking Modes | 36 | |

System PLLC1 Output Clocks | 39 | |

DDR PLLC2 Output Clocks | 43 | |

PLL and Reset Controller List | 48 | |

PLL and Reset Controller Registers | 48 | |

Peripheral ID Register (PID) Field Descriptions | 49 | |

Reset Type Status Register (RSTYPE) Field Descriptions | 49 | |

PLL Control Register (PLLCTL) Field Descriptions | 50 | |

PLL Multiplier Control Register (PLLM) Field Descriptions | 51 | |

PLL Controller Divider 1 Register (PLLDIV1) Field Descriptions | 51 | |

PLL Controller Divider 2 Register (PLLDIV2) Field Descriptions | 52 | |

PLL Controller Divider 3 Register (PLLDIV3) Field Descriptions | 52 | |

Oscillator Divider 1 Register (OSCDIV1) Field Descriptions | 53 | |

Bypass Divider Register (BPDIV) Field Descriptions | 54 | |

PLL Controller Command Register (PLLCMD) Field Descriptions | 55 | |

PLL Controller Status Register (PLLSTAT) Field Descriptions | 55 | |

PLL Controller Clock Align Control Register (ALNCTL) Field Descriptions | 56 | |

PLLDIV Ratio Change Status Register (DCHANGE) Field Descriptions | 57 | |

Clock Enable Control Register (CKEN) Field Descriptions | 58 | |

Clock Status Register (CKSTAT) Field Descriptions | 59 | |

SYSCLK Status Register (SYSTAT) Field Descriptions | 60 | |

DM643x DMP Default Module Configuration | 63 | |

Module States | 64 | |

IcePick Emulation Commands | 66 | |

PSC Interrupt Events | 66 | |

Power and Sleep Controller (PSC) Registers | 68 | |

Peripheral Revision and Class Information Register (PID) Field Descriptions | 69 | |

Interrupt Evaluation Register (INTEVAL) Field Descriptions | 69 | |

Module Error Pending Register 1 (MERRPR1) Field Descriptions | 70 | |

Module Error Clear Register 1 (MERRCR1) Field Descriptions | 70 | |

Power Domain Transition Command Register (PTCMD) Field Descriptions | 71 | |

Power Domain Transition Status Register (PTSTAT) Field Descriptions | 71 | |

Power Domain Status 0 Register (PDSTAT0) Field Descriptions | 72 | |

Power Domain Control 0 Register (PDCTL0) Field Descriptions | 73 | |

Module Status n Register (MDSTATn) Field Descriptions | 74 | |

Module Control n Register (MDCTLn) Field Descriptions | 75 | |

Power Management Features | 78 | |

TMS320DM643x DMP Master IDs | 88 | |

TMS320DM643x DMP Default Master Priorities | 89 | |

Reset Types | 92 | |

Document Revision History | 97 |

List of Tables | 7 |