www.ti.com

Clock Domains

4.2.2 Core Frequency Flexibility

The core frequency domain clocks are supplied by the PLL controller 1 (PLLC1). These domain clocks are flexible, to a degree, within the limitations specified in the

∙Input clock frequency range (MXI/CLKIN)

∙PLL1 multiplier (PLLM) range

∙PLL1 output (PLLOUT) frequency range based on the core voltage (1.05V or 1.2V) of the device

∙Maximum device speed

∙PLLC1's SYSCLK3:SYSCLK2:SYSCLK1 frequency ratio must be fixed to 1:3:6. For example, if SYSCLK1 is at 600 MHZ, SYSCLK2 must be at 200 MHZ, and SYSCLK3 must be at 100 MHZ.

As specified in the data manual, the PLLs can be driven by any input ranging from 20 to 30 MHZ. However, a 27 MHZ input is required if the video processing back end (VPBE) subsystem is needed to drive television displays with the integrated video DACs.

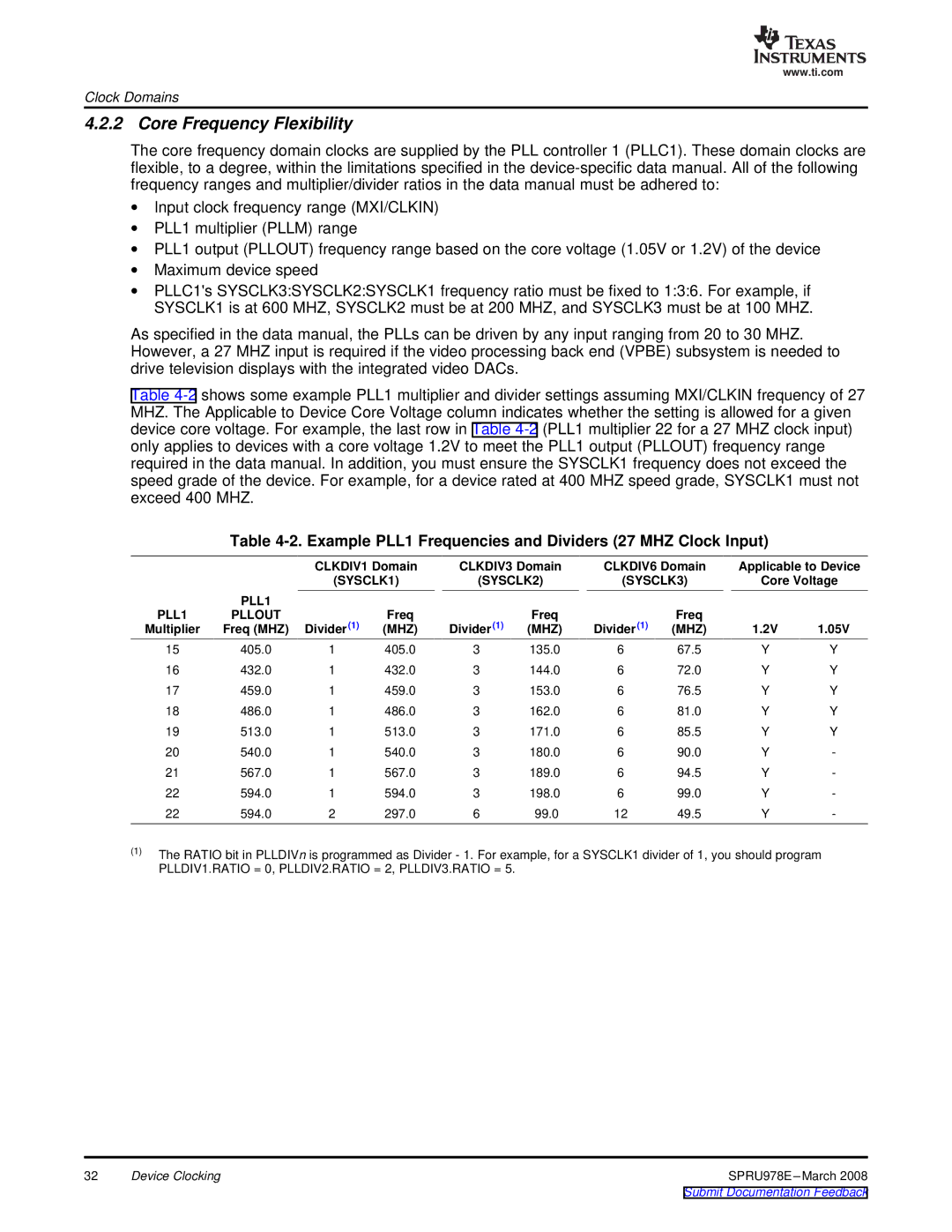

Table

Table 4-2. Example PLL1 Frequencies and Dividers (27 MHZ Clock Input)

|

| CLKDIV1 Domain | CLKDIV3 Domain | CLKDIV6 Domain | Applicable to Device | ||||

|

| (SYSCLK1) | (SYSCLK2) | (SYSCLK3) | Core Voltage | ||||

| PLL1 |

|

|

|

|

|

|

|

|

PLL1 | PLLOUT | Divider(1) | Freq | Divider(1) | Freq | Divider(1) | Freq |

|

|

Multiplier | Freq (MHZ) | (MHZ) | (MHZ) | (MHZ) | 1.2V | 1.05V | |||

15 | 405.0 | 1 | 405.0 | 3 | 135.0 | 6 | 67.5 | Y | Y |

16 | 432.0 | 1 | 432.0 | 3 | 144.0 | 6 | 72.0 | Y | Y |

17 | 459.0 | 1 | 459.0 | 3 | 153.0 | 6 | 76.5 | Y | Y |

18 | 486.0 | 1 | 486.0 | 3 | 162.0 | 6 | 81.0 | Y | Y |

19 | 513.0 | 1 | 513.0 | 3 | 171.0 | 6 | 85.5 | Y | Y |

20 | 540.0 | 1 | 540.0 | 3 | 180.0 | 6 | 90.0 | Y | - |

21 | 567.0 | 1 | 567.0 | 3 | 189.0 | 6 | 94.5 | Y | - |

22 | 594.0 | 1 | 594.0 | 3 | 198.0 | 6 | 99.0 | Y | - |

22 | 594.0 | 2 | 297.0 | 6 | 99.0 | 12 | 49.5 | Y | - |

(1)The RATIO bit in PLLDIVn is programmed as Divider - 1. For example, for a SYSCLK1 divider of 1, you should program PLLDIV1.RATIO = 0, PLLDIV2.RATIO = 2, PLLDIV3.RATIO = 5.

32 | Device Clocking | |

|

| Submit Documentation Feedback |