www.ti.com

Power Domain and Module States

6.3Power Domain and Module States

Note: The effects of DSP local reset and DSP module reset have not been fully validated; therefore, these resets are not supported and should not be used. Instead, the POR or RESET pins should be used to reset the entire DSP.

Table

6.3.1 Power Domain States

A power domain can only be in one of two states: ON or OFF, defined as follows:

∙ON: power to the power domain is on.

∙OFF: power to the power domain is off.

In the DM643x DMP, the AlwaysOn Power Domain is always in the ON state when the chip is

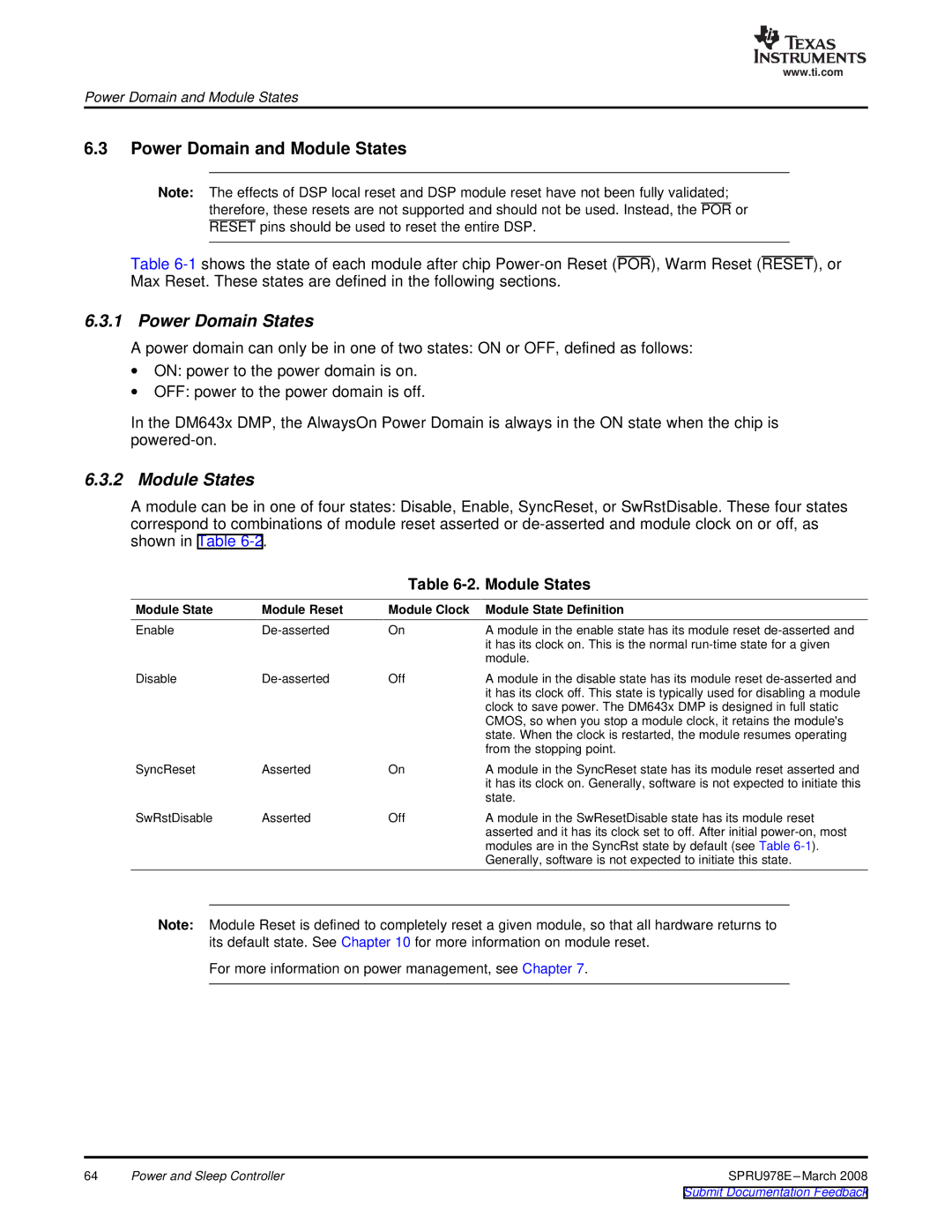

6.3.2 Module States

A module can be in one of four states: Disable, Enable, SyncReset, or SwRstDisable. These four states correspond to combinations of module reset asserted or

Table 6-2. Module States

Module State | Module Reset | Module Clock | Module State Definition |

Enable | On | A module in the enable state has its module reset | |

|

|

| it has its clock on. This is the normal |

|

|

| module. |

Disable | Off | A module in the disable state has its module reset | |

|

|

| it has its clock off. This state is typically used for disabling a module |

|

|

| clock to save power. The DM643x DMP is designed in full static |

|

|

| CMOS, so when you stop a module clock, it retains the module's |

|

|

| state. When the clock is restarted, the module resumes operating |

|

|

| from the stopping point. |

SyncReset | Asserted | On | A module in the SyncReset state has its module reset asserted and |

|

|

| it has its clock on. Generally, software is not expected to initiate this |

|

|

| state. |

SwRstDisable | Asserted | Off | A module in the SwResetDisable state has its module reset |

|

|

| asserted and it has its clock set to off. After initial |

|

|

| modules are in the SyncRst state by default (see Table |

|

|

| Generally, software is not expected to initiate this state. |

Note: Module Reset is defined to completely reset a given module, so that all hardware returns to its default state. See Chapter 10 for more information on module reset.

For more information on power management, see Chapter 7.

64 | Power and Sleep Controller |