www.ti.com

PLL Controller Registers

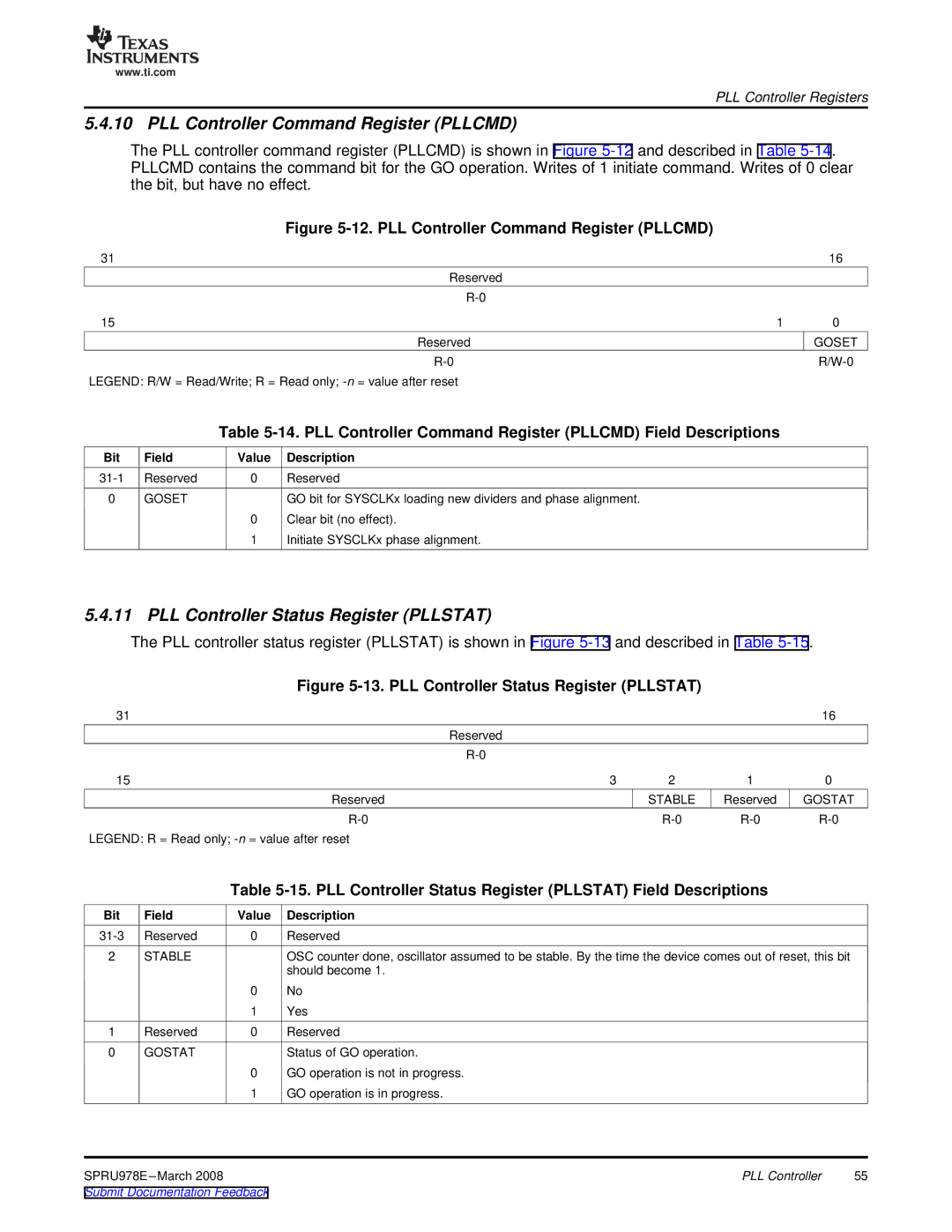

5.4.10 PLL Controller Command Register (PLLCMD)

The PLL controller command register (PLLCMD) is shown in Figure

Figure 5-12. PLL Controller Command Register (PLLCMD)

31 |

| 16 |

Reserved |

|

|

|

| |

15 | 1 | 0 |

Reserved |

| GOSET |

|

LEGEND: R/W = Read/Write; R = Read only;

Table

Bit | Field | Value | Description |

Reserved | 0 | Reserved | |

0 | GOSET |

| GO bit for SYSCLKx loading new dividers and phase alignment. |

|

| 0 | Clear bit (no effect). |

|

| 1 | Initiate SYSCLKx phase alignment. |

5.4.11 PLL Controller Status Register (PLLSTAT)

The PLL controller status register (PLLSTAT) is shown in Figure

Figure 5-13. PLL Controller Status Register (PLLSTAT)

31 |

|

|

| 16 |

| Reserved |

|

|

|

|

|

|

| |

15 | 3 | 2 | 1 | 0 |

Reserved |

| STABLE | Reserved | GOSTAT |

|

LEGEND: R = Read only;

Table

Bit | Field | Value | Description |

Reserved | 0 | Reserved | |

2 | STABLE |

| OSC counter done, oscillator assumed to be stable. By the time the device comes out of reset, this bit |

|

|

| should become 1. |

|

| 0 | No |

|

| 1 | Yes |

1 | Reserved | 0 | Reserved |

0 | GOSTAT |

| Status of GO operation. |

|

| 0 | GO operation is not in progress. |

|

| 1 | GO operation is in progress. |

PLL Controller | 55 | |

Submit Documentation Feedback |

|

|