UG144 April 24

LogiCORE IP Gigabit Ethernet MAC

Gigabit Ethernet MAC v8.5 User Guide

Date Version Revision

Revision History

DIS Product

Table of Contents

Designing with the Core

Configuration and Status

Appendix C Calculating DCM Phase-Shifting

Schedule of Figures

1Block Diagram

2External Gmii Receiver Logic for Spartan-3, Spartan-3E,

Figure A-2Frame Transfer across LocalLink Interface

DIS Product

Schedule of Tables

Clocking and Resetting Interfacing to Other Cores

About This Guide

Guide Contents

Typographical

Conventions

Preface About This Guide

Convention Meaning or Use Example

List of Acronyms

Online Document

Conventions

Acronym Spelled Out

Vhdl

Preface About This Guide Acronym Spelled Out

Introduction

Related Xilinx Ethernet Products and Services

About the Core

Recommended Design Experience

Technical Support

Specifications

Feedback

Gemac Core

System Overview

Core Architecture

Core Components

Gmac Core with Optional Management Interface

Core Interfaces

Core Interfaces

Core Architecture

Core Interfaces

Transmitter Interface

Client Side Interface

Flow Control Interface

Receiver Interface

MAC Unicast Address Optional

Management Interface Optional

Asynchronous Reset

Configuration Vector Optional

7Reset Signal Direction Clock Domain Description

Physical Side Interface

Mdio Interface

Graphical User Interface

Generating the Core

Parameter Values in the XCO File

Output Generation

Generating the Core

Designing with the Core

Using the Example Design as a Starting Point

General Design Guidelines

Design Steps

11-Gigabit Ethernet MAC Core Example Design

Designing with the Core

Implementing the 1-Gigabit Ethernet MAC in Your Application

Know the Degree of Difficulty

General Design Guidelines

Keep it Registered

Recognize Timing Critical Signals

Use Supported Design Flows

Make Only Allowed Modifications

1Abbreviations Used in Timing Diagrams Definition

Using the Client Side Data Path

Receiving Inbound Frames

Normal Frame Reception

Rxgoodframe, rxbadframe timing

Using the Client Side Data Path

Receiving Inbound Frames

Frame Reception with Errors

Vlan Tagged Frames

Client-Supplied FCS Passing

Enabled

Length/Type Field Error Checks

Disabled

Maximum Permitted Frame Length

5Receiver Statistics Vector Timing

Receiver Statistics Vector

DIS Product

Length see Maximum Permitted Frame

Normal Frame Transmission

Transmitting Outbound Frames

Padding

Transmitting Outbound Frames

7Frame Transmission with Client-supplied FCS

Client Underrun

9Transmission of a Vlan Tagged Frame

Inter-Frame Gap Adjustment

Transmitter Statistics Vector

10Inter-Frame Gap Adjustment

Name

Bit 31 is equivalent to bit

Overview of Flow Control

Using Flow Control

Flow Control Requirement

Flow Control Basics

Using Flow Control

Overview of Flow Control

Pause Control Frames

Transmitting a Pause Control Frame

Flow Control Operation of the Gemac

Core-initiated Pause Request

Client Initiated Pause Request

Core Initiated Response to a Pause Request

Receiving a Pause Control Frame

Client Initiated Response to a Pause Request

Flow Control Operation of the Gemac

Method

Flow Control Implementation Example

4Flow Control Implementation Triggered from Fifo Occupancy

Flow Control Implementation Example

Using Flow Control

Implementing External Gmii

Using the Physical Side Interface

Gmii Transmitter Logic

1External Gmii Transmitter Logic

Using the Physical Side Interface

Spartan-3, Spartan-3E, Spartan-3A and Virtex-4 Devices

Gmii Receiver Logic

Implementing External Gmii

DCM Reset circuitry

3External Gmii Receiver Logic for Virtex-5 Devices

Virtex-5 Devices

Rgmii Transmitter Logic

Implementing External Rgmii

Implementing External Rgmii

Virtex-4 Devices

5External Rgmii Transmitter Logic in Virtex-4 Devices

6External Rgmii Transmitter Logic in Virtex-5 Devices

Rgmii Receiver Logic

7External Rgmii Receiver Logic

Virtex-4 Devices

8External Rgmii Receiver Logic for Virtex-4 Devices

9External Rgmii Receiver Logic for Virtex-5 Devices

10RGMII Inband Status Decoding Logic

Rgmii Inband Status Decoding Logic

Connecting the Mdio to an Internally Integrated PHY

Using the Mdio interface

Connecting the Mdio to an External PHY

Using the Optional Management Interface

Configuration and Status

Host Clock Frequency

Configuration and Status

Configuration Registers

2Configuration Registers Address Description

Using the Optional Management Interface

Receiver Configuration

3Receiver Configuration Word Bit Default Description

Receiver Configuration Word

Interframe Gap Adjust Enable If ‘1,’ the transmitter will

Transmitter Configuration

6Flow Control Configuration Word Bit Default Description

Flow Control Configuration

Address Filter Configuration

Mdio Configuration

10Address Table Configuration Word Bits Default Description

Writing and Reading to and from the Configuration Registers

11 Address Table Configuration Word

12Address Filter Mode Bits Default Description

1Configuration Register Write Timing

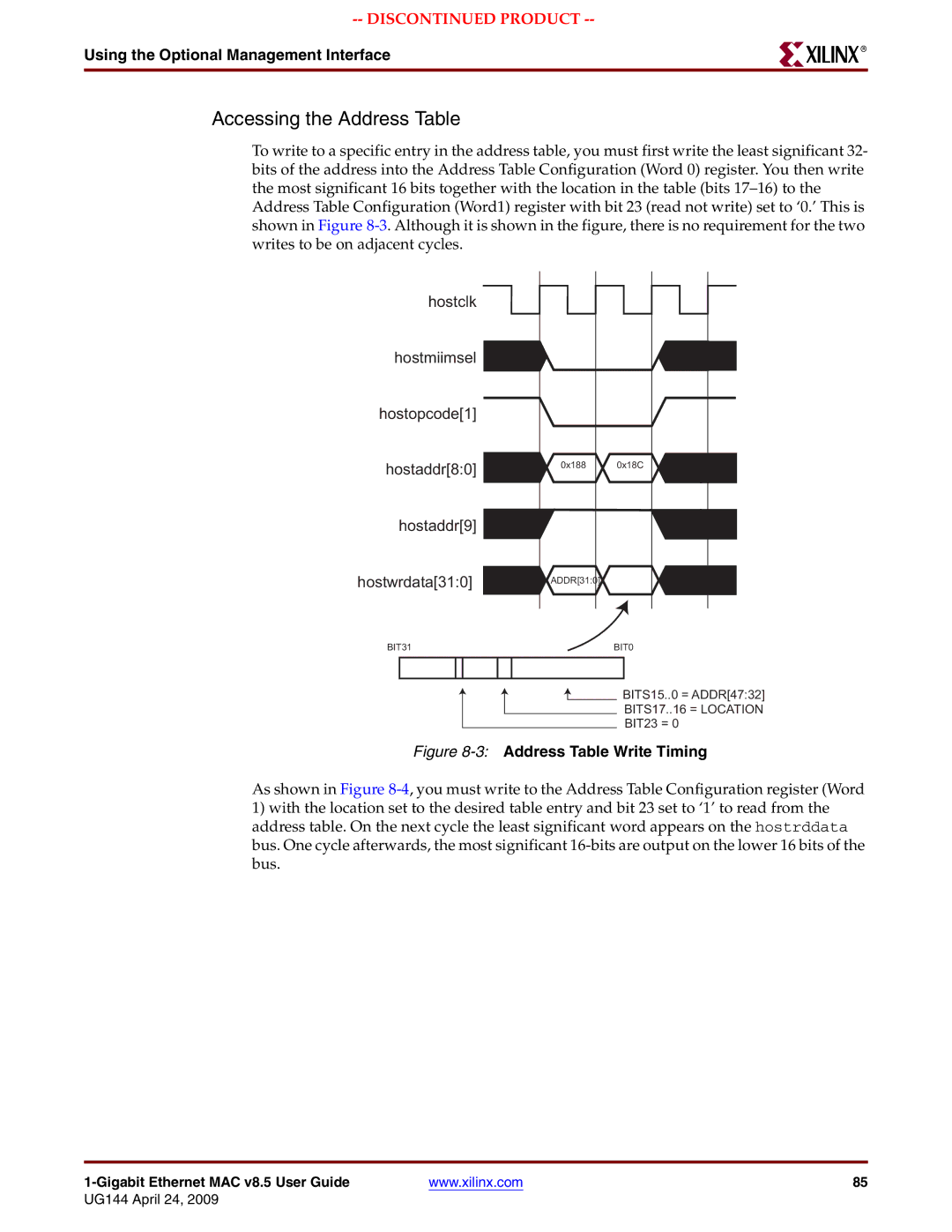

3Address Table Write Timing

Accessing the Address Table

Introduction to Mdio

Mdio Interface

5Typical MDIO-managed System

Write Transaction

Read Transaction

Accessing Mdio With Gemac

8MDIO Access through Management Interface

Pause frame MAC Source Address470

Access without the Management Interface

Transmitter Interframe Gap Adjust Enable

Receive Flow Control Enable . When this bit

Required Constraints

Constraining the Core

Constraining the Core

Period Constraints for Clock Nets

Required Constraints

Timespecs for Critical Logic within the Core

Timespecs for Reset Logic within the Core

Constraints when Implementing an External Gmii

Gmii IOB Constraints

1Input Gmii Timing Symbol Min Max Units

Gmii Input Setup/Hold Timing

Virtex-5 Devices

Virtex-5 devices with Delayed Data/Control

Understanding Timing Reports for Gmii Setup/Hold Timing

Non-Virtex-5 devices

Virtex-5 Devices with Delayed Clock

Rgmii IOB Constraints

Constraints when Implementing an External Rgmii

2Input Rgmii Timing Symbol Min Typical Units

Rgmii Input Setup/Hold Timing

Spartan-3, Spartan-3E, Spartan-3A, and Virtex-4 Devices

Rgmii DDR Constraints

Understanding Timing Reports for Rgmii Setup/Hold timing

106

4Timing Report Setup/Hold Illustration

108

Clocking the Core

Clocking and Resetting

With Internal Gmii

With External Gmii

Multiple Cores

Clocking and Resetting

With Rgmii

Standard Clocking Scheme

3Clock Management Logic with External Gmii Multiple Cores

Multiple Cores

4Clock Management Logic with External Rgmii Multiple Cores

Reset Conditions

Ethernet 1000Base-X PCS/PMA or Sgmii Core

Interfacing to Other Cores

Interfacing to Other Cores

Integration to Provide 1000BASE-X PCS with TBI

Ethernet 1000Base-X PCS/PMA or Sgmii Core

116

GTP

Virtex-5 LXT and SXT Devices

Clkdv

Virtex-5 FXT Devices

Integration to Provide Sgmii Functionality

Ethernet Statistics Core

Ethernet Statistics Core

120

Configuration Miim access Statistics Read

122

Implementing Your Design

Using the Simulation Model

Pre-implementation Simulation

Synthesis

XST-Verilog

Implementation

Generating the Xilinx Netlist

Mapping the Design

Placing-and-Routing the Design

Post-Implementation Simulation

Static Timing Analysis

Generating a Bitstream

Other Implementation Information

Using the Model

GMII/RGMII

Using the Client-Side Fifo

Interfaces

Appendix a Using the Client-Side Fifo

Transmit Fifo

Interfaces

Receive Fifo

Data Flow

Overview of LocalLink Interface

Clock Requirements

Functional Operation

Functional Operation

User Interface Data Width Conversion

Expanding Maximum Frame Size

Verification by Simulation

Core Verification, Compliance, and Interoperability

Hardware Verification

134

DCM Phase-Shifting

Calculating DCM Phase-Shifting

Finding the Ideal Phase-Shift

Appendix C Calculating DCM Phase-Shifting

Transmit Path Latency

Core Latency

Receive Path Latency

Appendix D Core Latency