Sparc JPS1

Release 1.0, 1 July Chapter

Page

Contents

Traps

Instructions

Implementation Dependencies

Sparc JPS1 Implementation-Dependent Traps

Memory Models

Level-1 Instruction Cache L1I Cache

Cache Organization 125 Cache Types

Fatal Error

Reset, REDstate, and errorstate 137 Reset Types

Error Handling 149 Error Classification

Asistchgerrorinfo

Index

UPA Programmer’s Model

General References

Page

Fonts and Notational Conventions

Overview

Navigating the SPARC64 V Implementation Supplement

High Reliability and High Integrity

SPARC64 V processor

Microarchitecture for High Performance

High Integration

Extended RAS interface to software

Advanced RAS features for caches

Advanced RAS features for the core

Component Overview

Asynchronous data error ADE trap for additional errors

SX-Unit

2Execution Unit Major Blocks

Instruction Control Unit IU

Execution Unit EU

1Instruction Control Unit Major Blocks

Storage Unit Major Blocks

Storage Unit SU

4Secondary Cache and External Access Unit Major Blocks

Secondary Cache and External Access Unit SXU

Instruction dispatch Synonym instruction initiation

Definitions

Issue-stalling

Sync Synonym machine sync

Page

Architectural Overview

Page

Please refer to , Data Formats in Commonality

Data Formats

Page

Nonprivileged Registers

Registers

FSRfloating-pointtraptype ftt

Floating-Point State Register FSR

FSRnonstandardfp NS

FSRversion ver

FSR Conformance

Privileged Registers

Tick Tick Register

Trap State Tstate Register

1shows the values for the VER register for SPARC64

Version VER Register

Ancillary State Registers ASRs

Performance Control Register PCR ASR

Ovro

OVF

Dispatch Control Register DCR ASR

Accessibility as described above impl. dep. #250

Registers Referenced Through ASIs

Performance Instrumentation Counter PIC Register ASR

VM70

PM70

Instruction Trap Register

Floating-Point Deferred-Trap Queue FQ

IU Deferred-Trap Queue

Data Watchpoint Registers

Data Prefetch

Instructions

Instruction Execution

Instruction Prefetch

1SPARC64 V Syncing Instructions

Syncing Instructions

Yes

Instruction Formats and Fields

2Instruction Fields Specific to SPARC64

Control transfer CTI

Instruction Categories

Control-Transfer Instructions CTIs

Call and Jmpl Instructions

Implementation-Dependent Instructions

Floating-Point Operate FPop Instructions

Instruction Fetch Stages

Processor Pipeline

Brhis

Execution Stages

Issue Stages

Completion Stages

Execution Stages for Cache Access

Please refer to .1 of Commonality

Traps

Processor States, Normal and Special Traps

REDstate Execution Environment

Errorstate

REDstate

REDstate Trap Table

Uses of the Trap Categories

Reset Traps

Trap Categories

Deferred Traps

Trap Type TT

Trap Control

Trap-Table Entry Addresses

PIL Control

Sparc JPS1 Implementation-Dependent Traps

Trap Processing

Exception and Interrupt Descriptions

Details of Supported Traps

Page

Sparc V9 Memory Model on

Memory Models

Synchronizing Instruction and Data Memory

Mode Control

Overview

Sparc V9 Memory Model

Release 1.0, 1 July Memory Models

Page

Table A-1Implementation-Specific Instructions

Instruction Definitions SPARC64 V Extensions

Page

Block Load and Store Instructions VIS

Invalid Valid

Implementation-Dependent Instructions

Call and Link

Format

Floating-Point Multiply-Add/Subtract

Page

Operation, and inexact, respectively

Non-Trapping cexc When FSR.NS =

Non-Trapping aexc When FSR.NS =

Jump and Link

Exceptions fpdisabled

Format 3 Ldda

Load Quadword, Atomic Physical

Memory Barrier

Bits in the cmask Field

Order Constraints Imposed by mmask Bits

01816

Partial Store VIS

Prefetch Data

Table A-7Prefetch Variants

Read State Register

Table A-7describes prefetch variants implemented in SPARC64

Store Barrier

Write State Register

Deprecated Instructions

Page

Traps Inhibiting Results

Floating-Point Nonstandard Mode

Ieee Std 754-1985 Requirements for

Fpexceptionother Exception ftt=unfinishedFPop

UnfinishedFPop Boundary Conditions

Denormalized number, eres is less than zero

Generates an unfinishedFPop exception

Table B-2unfinishedFPop Boundary Conditions

Pessimistic Zero

Table B-4Pessimistic Overflow Conditions

Operation Under FSR.NS =

Pessimistic Overflow

Table B-3Conditions for a Pessimistic Zero

UnfinishedFPop4

Floating-Point Exceptional Conditions and Results

Yes and op2 Nv, dNaN

Nonarithmetic Operations Under FSR.NS =

Page

Please refer to Section C.1 of Commonality

Implementation Dependencies

Definition of an Implementation Dependency

Please refer to Section C.2 of Commonality

Hardware Characteristics

Implementation Dependency Categories

List of Implementation Dependencies

Table C-1SPARC64 V Implementation Dependencies

Deferred traps

Reset trap

Entering errorstate on implementation-dependent errors

Errorstate processor state

Floating-point underflow detection

Data access FPU trap

Clean windows trap

Flush instruction

Unimplemented LDD trap

SIRenable control flag

MMU disabled prefetch behavior

IMPDEPn instructions

Implementation-dependent memory model

Implicit ASI when TL

Unimplemented values for PSTATE.MM

Coherence and atomicity of memory operations

Table C-1SPARC64 V Implementation Dependencies 7

Table C-1SPARC64 V Implementation Dependencies 8

Table C-1SPARC64 V Implementation Dependencies 9

Table C-1SPARC64 V Implementation Dependencies 10

258

255

256

257

Please refer to Appendix D of Commonality

Formal Specification of the Memory Models

Page

Instruction65

Opcode Maps

Page

Virtual Address Translation

Memory Management Unit

Table F-1Organization of SPARC64 V TLBs

Translation Table Entry TTE

Release 1.0, 1 July Chapter F Memory Management Unit

TSB Pointer Formation

TSB Organization

TSB Pointer Formation

TLB miss 64 16-67

Faults and Traps

Instructionaccessexception

Reset, Disable, and REDstate Behavior

Asimcntl Memory Control Register

Accessing MMU Registers

Access Modes Supervisor read/write

Internal Registers and ASI operations

JPS1TSBP

10.4 I/D TLB Data In, Data Access, and Tag Read Registers

Table F-3MCNTL Field Description

RMD

Page

TLB#

Table F-4MMU TLB Data Access Address Assignment

Kbyte page entry

MMU TLB Tag Access Register

TSB Base Registers

10.9 I/D Synchronous Fault Status Registers I-SFSR, D-SFSR

MMU I/D Synchronous Fault Status Registers I-SFSR, D-SFSR

10.7 I/D TSB Extension Registers

EID

Table F-5I-SFSRBit Description

SFSRBit Description

FT60 Error Description

Table F-6describes the field encoding for ISFSR.FT

Table F-8D-SFSRBit Description 1

Isfsr Update Policy

Table F-8D-SFSRBit Description 2

SFSRBit Description 3

Table F-9defines the encoding of the FT60 field

Fresh fault or miss3

MMU Synchronous Fault Status Register FT Fault Type Field

Dsfsr Update Policy

Table F-11Bypass Attribute Bits on SPARC64

Table F-10DSFSR Update Policy

MMU Bypass

Kbytes

Restriction of sTLB Entry Direct Replacement

TLB Replacement Policy

Automatic TLB Replacement Rule

Page

Please refer to Appendix G of Commonality

Assembly Language Syntax

Page

Please refer to Appendix H of Commonality

Software Considerations

Page

Please refer to Appendix I of Commonality

Extending the Sparc V9 Architecture

Page

Please refer to Appendix K of Commonality

Changes from Sparc V8 to Sparc

Page

Please refer to Appendix J of Commonality

Programming with the Memory Models

Page

SPARC64 V ASI Assignments 1

Address Space Identifiers

SPARC64 V ASI Assignments

TBD

SPARC64 V ASI Assignments 2

SPARC64 V ASI Assignments 3

Special Memory Access ASIs

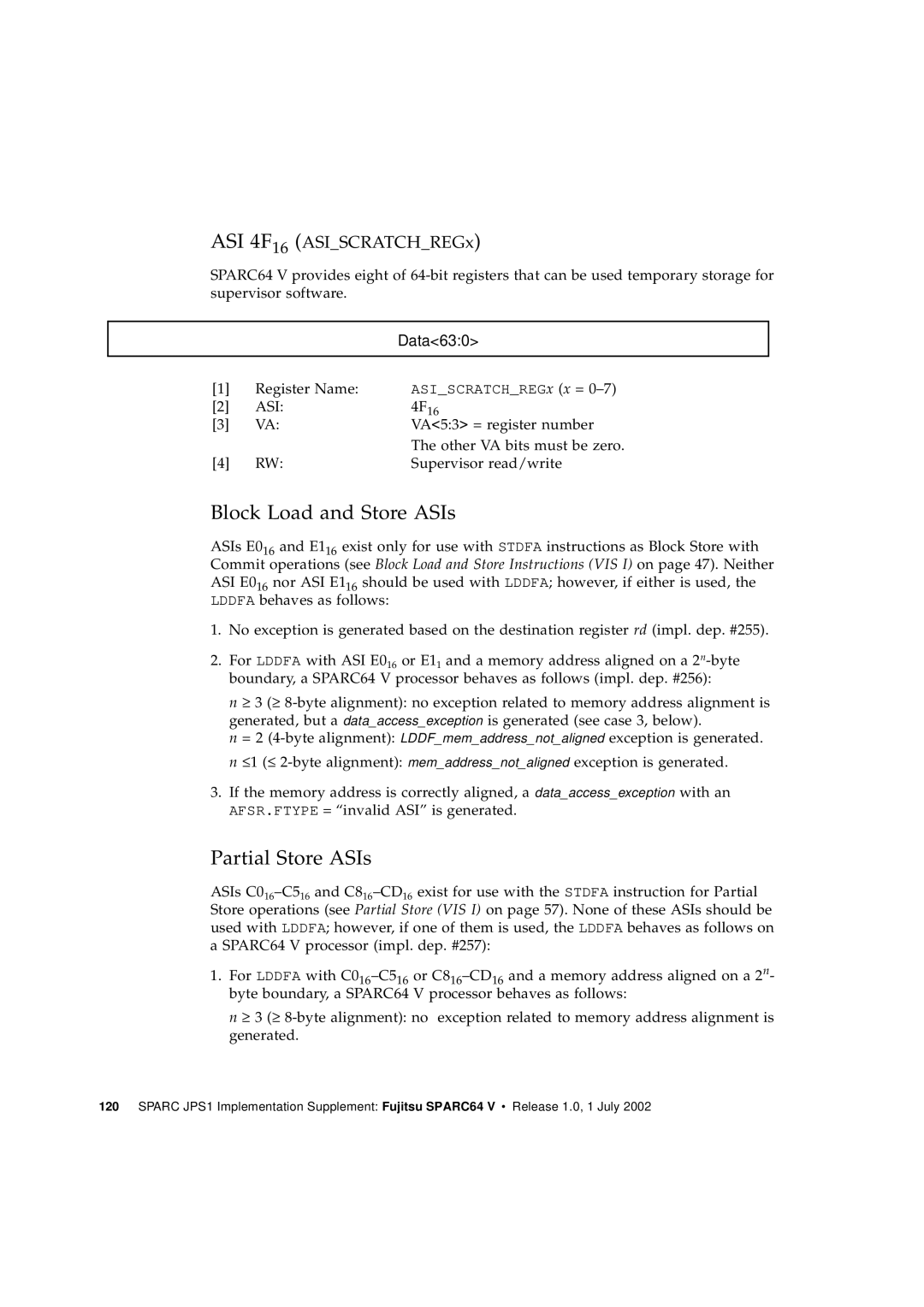

Partial Store ASIs

Block Load and Store ASIs

High-Speed Lbsy Read Mechanism

Barrier Assist for Parallel Processing

Interface Definition

Lbsy Control Register ASICLBSYR0, ASICLBSYR1

ASI Registers

High-Speed BST Write Mechanism

Bstw Busy Status Register Asicbstwbusy

Bstw Control Register ASICBSTW0, ASICBSTW1

Read Write is ignored

Last Barrier Synchronization Status Read ASILBSYR0

Barrier State Write ASIBSTW0, ASIBSTW1

EF16

Cache Types

Cache Organization

Level-1 Instruction Cache L1I Cache

Table M-1L1I Cache Characteristics

Level-2 Unified Cache L2 Cache

Table M-2L1D Cache Characteristics

Table M-3L2 Cache Characteristics

Level-1 Data Cache L1D Cache

Table M-5L2 Cache Moesi States

Cache Coherency Protocols

Cache Control/Status Instructions

Table M-4Relationships Between Cache Coherency Protocols

ASIFLUSHL1I

Flush Level-1 Instruction Cache

Table M-6ASIL2CTRL Register Bits

3 L2 Diagnostics Tag Read

Level-2 Cache Control Register ASIL2CTRL

ASIL2DIAGTAGREADREG

4 L2 Diagnostics Tag Read Registers

Page

Interrupt Dispatch

Interrupt Handling

Membar

Figure N-2is an example of the interrupt receive flow

Interrupt Receive

Interrupt Vector Dispatch Status Register

Interrupt Global Registers

Interrupt-Related ASR Registers

Interrupt Vector Dispatch Register

Appendix contains these sections

Reset, REDstate, and errorstate

Reset Types

Power-on Reset POR

Software-Initiated Reset SIR

Watchdog Reset WDR

Externally Initiated Reset XIR

Figure O-1illustrates the processor state transition diagram

REDstate and errorstate

PA = 000007FFF000000016

Floating Point registers

Processor State after Reset and in REDstate

CPU Fatal Error state

Integer registers

Mask dependent

TBA6315

Counter

Table O-2ASR State after Reset and in REDstate

ASI Register State After Reset and in REDstate 1

Others

ASI Register State After Reset and in REDstate 2

ASI Register State After Reset and in REDstate 3

11011 Unchanged

Operating Status Register Opsr

To be defined later

Hardware Power-On Reset Sequence

Firmware Initialization Sequence

Page

Fatal Error

Error Handling

Error Classification

Instruction-Obstructing Error

Errorstate Transition Error

Urgent Error

Urgent Error Independent of Instruction Execution

Correctable Error CE, corrected by hardware

Restrainable Error

Traps for Urgent Errors

Table P-1Registers Related to Error Handling

Action and Error Control

Registers Related to Error Handling

Following registers are related to the error handling

Table P-2Action Upon Detection of an Error 1

Summary of Actions Upon Error Detection

Table P-2summarizes what happens when an error is detected

Deviation in SPARC64

Table P-2Action Upon Detection of an Error 2

Ideal specification

Table P-2Action Upon Detection of an Error

Error Marking for Cacheable Data

Error Marking for Cacheable Data Error

Table P-4Format of Error-Marked Data

Format of Error-Marking Data

Table P-3Syndrome for Data Marked for Error

Table P-5ERRORMARKID Bit Description

Table P-6shows the Errormarkid set by the CPU

Table P-7Error Marking on SPARC64 IV and SPARC64

Difference Between Error Marking on SPARC64 IV

Rteue

Control of Error Action Asierrorcontrol

Value in ASIERRORCONTROL, as defined in Table P-9

Table P-8 Asieidr Bit Description

Ugehandler

Weaked

Always 0 Eeother

Fatal Error and errorstate Transition Error

Table P-10Format of Asistchgerrorinfo Bit Description

4C16

Current SPARC64 V implementation

Fatal Error Types

Types of errorstate Transition Errors

Table P-11ASIUGESR Bit Description 1

Urgent Error

Ideal specification not implemented

Table P-11ASIUGESR Bit Description 2

Table P-11ASIUGESR Bit Description 3

Instend Priv Mugedae Mugeiae Mugeiuge

Action of asyncdataerror ADE Trap

Conditions that cause ADE trap

Table P-11ASIUGESR Bit Description 4

State transition

Set the specific register setting

Following three sets of registers are updated

Following actions are executed in this order

Instend

Update of ASIUGESR, as shown in Table P-13

Instruction End-Method at ADE Trap

Upon completion of a Retry or Done instruction

Expected Software Handling of ADE Trap

Void ExpectedsoftwarehandlingofADEtrap

See Appendix F, Memory Management Unit, for details

Instruction Access Errors

Data Access Errors

Asiasyncfaultstatus Asiafsr

Restrainable Errors

Ceincomed

DGL1$U2$STLB

Implementation Deviation SPARC64 V sets

Uedstbeto

UERAWL2$FILL

UERAWL2$INSD

WAY

Contents

Syndrome

ASIASYNCFAULTADDRU2 register is described in Table P-17

Contents of PABIT423

Expected Software Handling of Restrainable Errors

Page

Terminology used in Table P-18is defined as follows

Handling of Internal Register Errors

Register Error Handling Excluding ASRs and ASI Registers

Table P-18shows error handling for most registers

ADE trap, W

ASR Error Handling

Table P-19shows the handling of ASR errors

Table P-19ASR Error Handling

Parity Always

ASI Register Error Handling

Error Protect

Terminology used in Table P-20is defined as follows

Error Detect Condition

Correction

Error Type

Table P-20Handling of ASI Register Errors

Table P-20shows the handling of ASI register errors

Table P-20Handling of ASI Register Errors

Error in D1 Cache Tag and I1 Cache Tag

Cache Error Handling

Handling of a Cache Tag Error

SPARC64 V Implementation and the Ideal Specification

Error in U2 Unified Level 2 Cache Tag

Correctable Error in D1 Cache Data

Handling of an I1 Cache Data Error

Handling of a D1 Cache Data Error

Marked Uncorrectable Error in D1 Cache Data

Raw Uncorrectable Error in U2 Cache Data

Handling of a U2 Cache Data Error

Correctable Error in U2 Cache Data

Marked Uncorrectable Error in U2 Cache Data

I1 Cache Way Reduction

Automatic Way Reduction of I1 Cache, D1 Cache, and U2 Cache

Way Reduction Condition

U2 Cache Way Reduction

D1 Cache Way Reduction

Table P-22Error Protection and Detection of TLB Entries

TLB Error Handling

Handling of TLB Entry Errors

Error in TLB Entry Detected on Ldxa Instruction Access

Automatic Way Reduction of sTLB

STLB Way Reduction

Handling of Extended UPA Bus Interface Error

Handling of Extended UPA Address Bus Error

Handling of Extended UPA Data Bus Error

Correctable Error on Extended UPA Data Bus

UE in Outgoing Data to Extended UPA Data Bus

Page

Counter Clear/Set

Performance Instrumentation

Performance Monitor Overview

Sample Pseudocodes

Counter Stop and Read

Counter Event Selection and Start

Table Q-1Events and Encoding of Performance Monitor

Performance Monitor Description

Events and Encoding of Performance Monitor

Instruction Statistics

Counts the committed Floating Multiply-and-Add instructions

Instruction Count instructioncounts

Trap-Related Statistics

Counts the occurrences of data uTLB misses

MMU Event Counters

Counts the occurrences of Tcc instructions

Counts the occurrences of instruction uTLB misses

Counts the total latency of I1 cache misses

Cache Event Counters

Counts the occurrences of I1 cache misses

Counts the occurrences of D1 cache misses

Counts L2 cache references by demand read access

Counts the occurrences of L2 cache miss by demand access

Counts the number of Scpbreq packets received

UPA Event Counters

Counts the number of Sinvreq packets received

Counts the number of Scpireq packets received

Barrier-Assist ASI Read Count asirdbar

Miscellaneous Counters

Page

Table R-1CPU’s UPA Port Slave Area Mapping

UPA Programmer’s Model

Mapping of the CPU’s UPA Port Slave Area

Table R-1shows the mapping of the CPU’s UPA port slave area

Table R-2UPA PortID Register Fields

UPA PortID Register

Upacap

UPA Config Register

Table R-3UPA Config Register Description

UPA PortID Register Fields

UPA Config Register Description

Upccap

Pcon

UPCCAP2

MID

Page

SPARC64 V and UltraSPARC-III Differences 1

Summary of Differences between SPARC64 V and UltraSPARC-III

UPA

Table T-1SPARC64 V and UltraSPARC-III Differences 2

Sfsr

Table T-1SPARC64 V and UltraSPARC-III Differences 3

Page

Please refer to Bibliography in Commonality

Bibliography

General References

Page

Auge

Index

Page

ASIINTRW133

Page

DAE

Error detection action155

DGL1$L2$STLB error194 DGL1$U2$STLB error195

Dmmu

On Jmpl instruction error53 update during MMU trap90

Persistence38

ECCerror exception46, 153, 155

Statistics monitoring206-207

FSR

FQ17

Immu

Isfsr

Update during MMU trap90

PSO41 RMO41

Lddfa instruction80

OBP

Release 1.0, 1 July Chapter Index

PTE

Release 1.0, 1 July Chapter Index

Page

TLB

UnimplementedFPop floating-point trap type70

UITLB10, 85, 90 uncorrectable error152

Way reduction194 uDTLB10, 85