HP Integrity rx3600

Copyright 2007 Hewlett-Packard Development Company, L.P

Table of Contents

Installing the System

Cfggen Operation

Installing the Server into a Pedestal Mount

Cfggen Utility

Starting Cfggen

123

Update

139

VRM

177

Installing a PCI/PCI-X/PCIe Card Offline

Removing a Hot-Swappable Power Supply

Replacing a Hot-Swappable Power Supply

Online Replacement OLR

261

257

283

317

306

Ioconfig

Boottest

Cpuconfig

Conconfig

351

Page

Front Panel LEDs

List of Figures

OS Reinstallation Flowchart

Processor Board Assembly

Processor Power Cable

Board Assembly

General Diagnostic Tools List

External Health LED States

VFP External Health Description

Server Drives

Processor Upgrades

List of Examples

Page

Document Organization

Intended Audience

New and Changed Information in This Edition

Publishing History

Typographic Conventions

Warranty Information

Related Documents

Related Information

HP Encourages Your Comments

Diagnostics and Event Monitoring Hardware Support Tools

Page

Server Subsystems

Overview

I/O Subsystem Block Diagram

PCI/PCI-X I/O Rope Groups

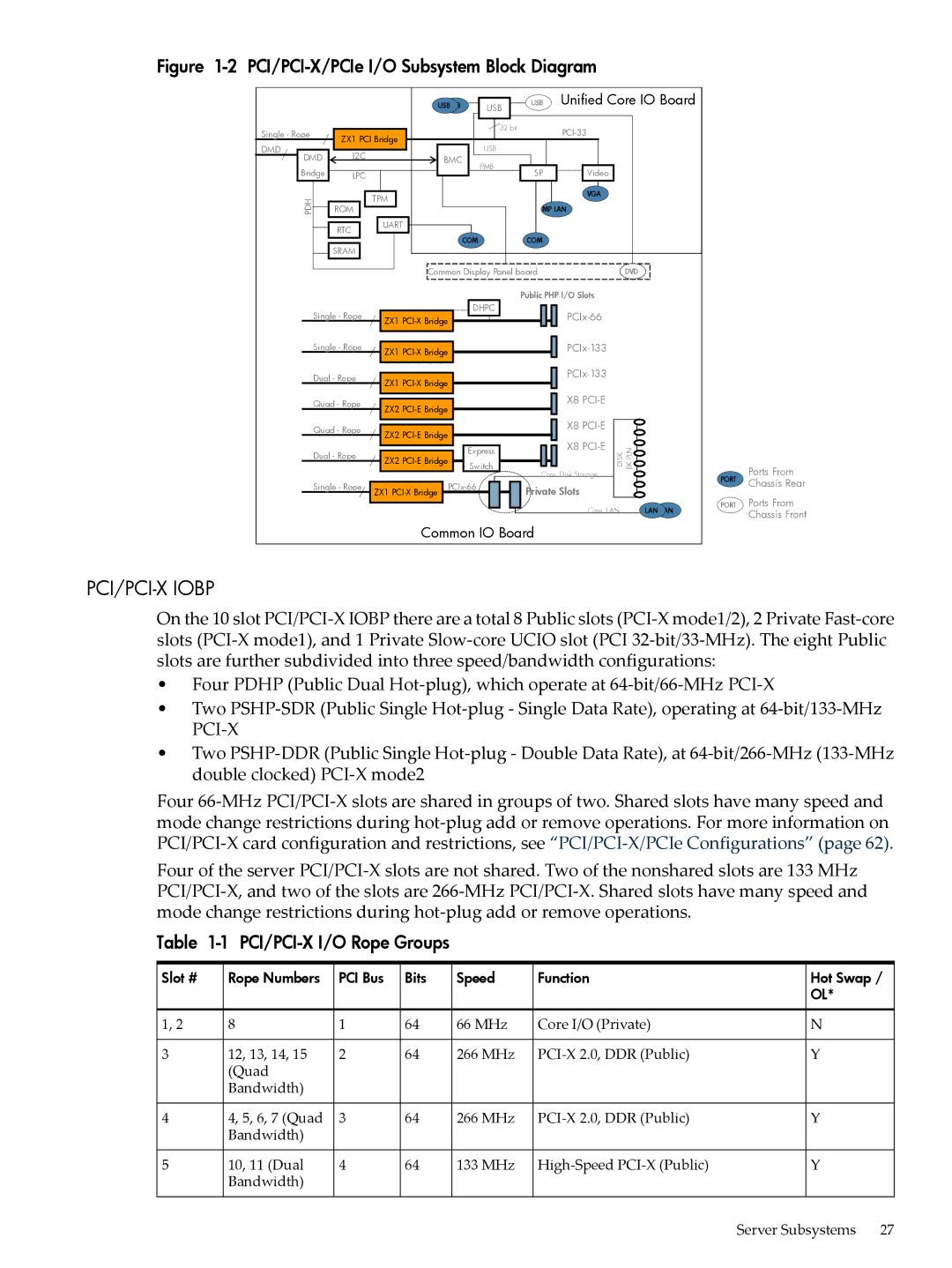

PCI/PCI-X/PCIe I/O Subsystem Block Diagram

PCI/PCI-X/PCIe Iobp

PCI/PCI-X/PCIe I/O Rope Groups

PCIe MPS Optimization

Server supports the following Dimm sizes 512-MB

Supported Memory Configurations

Processor

Memory

8-DIMM Memory Carrier Block Diagram

Cooling

24-DIMM Memory Carrier Block Diagram

Cooling Fans

Power

Power Subsystem Block Diagram

Mass Storage

Front Display Panel, DVD, and Diagnostic Panel

Event IDs for Errors and Events

Firmware

User Interface

Controls, Ports, and LEDs

Front Panel

4lists the front panel controls and LED states

9shows the front control panel LEDs

Front Panel Controls and LEDs

Storage and Media Devices

Hot-Pluggable Disk Drive LEDs

Hot-Pluggable Disk Drive LEDs

Diagnostic Panel

Hot-Pluggable Disk Drive Slot Availability LEDs

DVD Drive

Rear Panel

12 Diagnostic Panel Label and LEDs

13 Rear Panel Control, Port, and LED Locations

ILO 2 MP

14 Core I/O Board Controls, Ports, and LEDs

ILO 2 MP Reset Button

ILO 2 MP Status and LAN LEDs

System LAN

Core I/O Board Ports

ILO 2 MP Status LEDs

Power Supply

Rear Panel UID/Locator LED and Button

PCI/PCI-X/PCIe Card Slot

Controls, Ports, and LEDs

Page

Server Specifications

Server Specifications

Grounding

Dimensions and Values

Electrical Specifications

System Power Specifications

Additional Component Power Consumption

Physical and Environmental Specifications

Power Consumption and Cooling

4lists additional component power consumption

Ashrae

Physical and Environmental Specifications

Page

Page

Safety Information

Installing the System

Verifying Site Preparation

Installation Sequence and Checklist

Installation Sequence Checklist

Unpacking and Inspecting the Server

Returning Damaged Equipment

Inspecting the Shipping Containers for Damage

Unpacking the Server

Checking the Inventory

Installing Additional Components

Removing and Replacing the Top Cover

Removing the Top Cover

Removing and Replacing the Memory Carrier Assembly Cover

Removing the Memory Carrier Assembly Cover

Replacing the Top Cover

Installing a Hot-Swappable Power Supply

Replacing the Memory Carrier Assembly Cover

Power Supply Loading Guidelines

Removing and Replacing Hot-Swappable Disk Drive Fillers

Installing a Hot-Swappable Power Supply

Replacing a Hot-Swappable Disk Drive Filler

Installing a Hot-Pluggable Disk Drive

Installing a Hot-Pluggable Disk Drive

Removing a Hot-Swappable Disk Drive Filler

Installing a Hot-Pluggable Disk Drive

Section contains the following topics

Installing a PCI/PCI-X/PCIe Card

PCI/PCI-X/PCIe Configurations

Slot

Shared Slots

PCI/PCI-X/PCIe Iobp

PCI 66 MHz

Offline Installation of a PCI Card

To remove the memory carrier assembly, follow these steps

Removing and Replacing the Memory Carrier Assembly

Removing the Memory Carrier Assembly

Supported Memory Carrier Assembly Configurations

Removing and Replacing the Memory Carrier Assembly

Replacing the Memory Carrier Assembly

Memory Carrier Assembly with Side Cover Removed

Installing System Memory DIMMs

5lists the 8-DIMM memory carrier load order

Memory Installation Conventions

Supported Dimm Sizes and Memory Configurations

Memory Load Order

8-DIMM Memory Carrier Board Slot IDs

9shows the Dimm slot IDs for the 8-DIMM memory carrier board

Installing the System

24-DIMM Memory Carrier Loading Examples

Installing Memory

11 Inserting a Dimm into the Memory Board Connector

Removing the Processor Board Assembly

Removing and Replacing the Processor Board Assembly

Replacing the Processor Board Assembly

Installing a Dual-Core Processor

Processor Load Order

Installing a Dual-Core Processor

Processor Load Order

Required Tools

Installing the System

13 Processor Board Assembly Front View

Installing the Server into a Pedestal Mount

Installing the Server into a Rack or Pedestal Mount

Connecting the Cables

Installing the Server into a Rack

AC Input Power

Power States

Power States

Applying Standby Power to the Server

Console Setup

Elements Required to Start a Console Session

Overview

Setup Checklist

Console Setup Flowchart

10 Setup Checklist

Preparation

Determining the Physical iLO 2 MP Access Method

18shows the server rear ports

11 Physical Connection Matrix

Configuring the iLO 2 MP LAN Using Dhcp and DNS

Determining the iLO 2 MP LAN Configuration Method

12 LAN Configuration Methods

Mp0014c29c064f

Configuring the iLO 2 MP LAN Using ARP Ping

Arp -s

13 ARP Ping Commands

Ping

Configuring the iLO 2 MP LAN Using the RS-232 Serial Port

Following is the MP Main Menu

Additional Setup

Modifying User Accounts and Default Password

Logging In to the iLO 2 MP

Security Access Settings

Setting Up Security

Accessing the Host Console

Accessing the iLO 2 MP With the Web Browser

Web browser access is an embedded feature of the iLO 2 MP

Help

Accessing the Host Console With the TUI CO Command

Power States

Powering On and Powering Off the Server

Accessing the Host Console with the Smash SM CLP

Accessing the Graphic Console Using VGA

14 Power States

Powering On the Server

Powering On the Server Using the iLO 2 MP

Powering On the Server Manually

Powering Off the Server Manually

Core I/O Card Configuration

Powering Off the Server

Powering Off the Server Using the iLO 2 MP

Global Hot Spare

Integrated RAID

HP 8 Internal Port SAS HBA SAS Controller

Integrated Mirror

Press Enter To update the firmware, use the mptutil command

15 Mptutil Commands and Functions

Flashing Firmware on First Controller

Drvcfg Utility

EFI Commands

List screen also identifies the adapter

Type drvcfg -sand press Enter

Value

Esc

0xFF, 0 255 decimal

Disabled or error

Error

Adapter. Viewing and modifying settings for the adapter is

Currently supported type is IR.l

Or will discontinue control of the adapter upon reload

Be limited

Primary drive

Device does not meet the minimum requirements for use

An IM array

Device is not large enough to mirror existing data on

Secondary

Field is grayed out under the following conditions

Array

Primary

Is grayed out under the following conditions

Manage Array Screen

From this directory use cfggen

Cfggen Utility

Starting Cfggen

Change to the directory that containscfggen.efi

Cfggen Operation

Rules for creating IM volumes and hot spare disks

Cfggen Commands

Quick synchronization of the volume created

EnclBay

Available

Controller # SAS controller number between 0

To specify hot-spare creation

Quick Installation Procedure

Connecting External Storage

Smart Array P400, P600 and P800 Controllers

You can use the following operations with saupdate

Saupdate Utility

Power on the enclosure Power on the server

Saupdate operation parameters

List

Update all

Help or ?

Error Messages

25 Ebsu Welcome Screen

Ebsu Utility

27 Ebsu Maintain Firmware Screen

Configuring the Array

17 ACU and Orca Supported Features and Procedures

Comparing the Utilities

Orca Utility

29 Orca Main Menu Creating a Logical Drive Using Orca

Installation Troubleshooting

Troubleshooting Methodology

ACU Utility

19 Server Power Button Functions When Server is Off

Troubleshooting Using the Server Power Button

Server Does Not Power On

18 Server Power Button Functions When Server is On

DVD Problems

Operating System Does Not Boot

Operating System Boots with Problems

Intermittent Server Problems

Introduction

Console Problems

Installing the Latest Version of the Firmware

Enabling the Trusted Platform Module

Enabling the TPM

Power on the server. See Powering On the Server

122

Boot Options List

Configuring System Boot Options

Booting and Shutting Down HP-UX

Autoboot Setting

Adding HP-UX to the Boot Options List

Booting HP-UX From the EFI Boot Manager

Booting HP-UX in Standard Mode

Booting HP-UX From the EFI Shell

Hpux boot -is vmunix

Booting HP-UX in Single-User Mode

Shutting Down HP-UX

Booting HP-UX in LVM-Maintenance Mode

Adding HP OpenVMS to the Boot Options List

Booting and Shutting Down HP OpenVMS

Booting HP Open VMS

Booting HP OpenVMS from the EFI Boot Manager

Booting HP OpenVMS from the EFI Shell

Fs5 \efi\vms\vmsloader.efi

Shutting Down HP OpenVMS

Adding Microsoft Windows to the Boot Options List

Booting and Shutting Down Microsoft Windows

Fs0\ msutil\nvrboot

Booting the Microsoft Windows Operating System

Shutting Down Windows from the Start Menu

Shutting Down Windows from the Command Line

From 0-600, with a default

Shutting Down Microsoft Windows

Booting and Shutting Down Linux

Adding Linux to the Boot Options List

For example

Booting the Red Hat Enterprise Linux Operating System

Booting the SuSE Linux Enterprise Server Operating System

Booting Red Hat Enterprise Linux from the EFI Shell

Booting SuSE Linux Enterprise Server from the EFI Shell

Shutting Down Linux

Methodology

General Troubleshooting Methodology

Recommended Troubleshooting Methodology

Troubleshooting Entry Points

Basic and Advanced Troubleshooting Tables

RED Amber

Front Panel LED States

Basic Entry Class Troubleshooting

Is flashing red and internal

Panel LEDs indicate that

OS is non-responsive hung

Advanced Entry Class Troubleshooting

Troubleshooting Tools

LEDs

Front Panel

Internal Health LED

External Health LED

External Health LED States

VFP External Health Description

System Health LED States

Internal Health LED States

VFP Internal Health Description

System Health LED

Unit Identifier Button/LED

Diagnostics Panel LEDs

11lists diagnostic panel LED states

10 VFP System Health Description

Customer Replaceable Unit Health LEDs

Diagnostics

Online Diagnostics and Exercisers

Diagnostics Panel LED States

Online Support Tools List

Linux Online Support Tools

Offline Support Tools List

Online Support Tool Availability

14lists genearl diagnostic tools

General Diagnostic Tools

Fault Management Overview

HP-UX Fault Management

To access iLO 2 MP event logs, follow these steps

Errors and Reading Error Logs

Using Event Logs

Accessing iLO 2 MP Event Logs

Supported Configurations

System Block Diagram

This section provides a system build-up procedure

Rx3600 with PCI/PCI-X I/O System Block Diagram

Rx3600 with PCI/PCI-X/PCIe I/O System Block Diagram

CPU, Memory and SBA

System Build-Up Troubleshooting Procedure

Troubleshooting the rx3600 CPU

FP and Diagnostic LED board HBAs optional

Processor Module Behaviors

Processor Problem Identification

15 Processor Events that Light Diagnostic Panel LEDs

Itanium Processor Load Order

Processor Events That May Light Diagnostic Panel LEDs

Troubleshooting rx3600 Memory

Memory Error Messages

Memory Dimm Load Order

Memory Subsystem Behaviors

Memory Subsystem Events that Light Diagnostic Panel LEDs

5shows the Dimm slot IDs for the 8-DIMM memory carrier board

Troubleshooting rx3600 SBA

System Power BPS and I/O VRM

Power Subsystem Behavior

System Power LED/Switch

Power LED States

Cooling Subsystem Behavior

Power Supply Power LED

20lists the power supply LED states

Cooling Subsystem

Messages

23 I/O Card Events that Light Diagnostic Panel LEDs

Common I/O Backplane

Subsystem Behavior

Card Events that May Light Diagnostic Panel LEDs

PCI/PCI-X/PCIe Slot-Rope-ACPI Paths

24 I/O Card Events that May Light Diagnostic Panel LEDs

25and list the PCI slot-rope-ACPI paths

PCI/PCI-X Slot-Rope-ACPI Paths

Management subsystem consists of the iLO 2 MP and the BMC

Manageability Reset Button

Management Subsystem

Manageability LAN LED

28 Manageability Status LED

Subsystem

Manageability Status LED

Verifying Hard Disk Drive Operation

HBA Bulkhead LAN LEDs

LAN a Connector LEDs

LAN B Connector LEDs

LAN LEDs

31 Normal Boot Process LED States

Booting

Identifying and Troubleshooting Firmware Problems

Firmware Updates

Server Interface

Environment

Reporting Your Problems to HP

Troubleshooting the Server Interface

32 rx3600 Environmental Specifications

Online Support

Phone Support

Collecting Information Before Contacting Support

Removing and Replacing Server Components

Required Service Tools

Hot-Swappable Components

HP Integrity rx3600 Component Classification

Accessing a Rack-Installed Server

Hot-Pluggable Components

Cold-Swappable Components

Accessing a Pedestal-Installed Server

Extending the Server from the Rack

Inserting the Server into the Rack

Removing the Top Cover

Removing and Replacing the Top Cover

Replacing the Top Cover

Removing and Replacing the Memory Carrier Assembly Cover

Replacing the Memory Carrier Assembly Cover

Removing the Memory Carrier Assembly Cover

Removing a Hot-Swappable Chassis Fan Unit

Removing and Replacing a Hot-Swappable Chassis Fan Unit

Pull the fan straight up and out of the chassis

Replacing a Hot-Swappable Chassis Fan Unit

Removing and Replacing a Hot-Swappable Power Supply

Power Supply Loading Guidelines

Removing a Hot-Swappable Power Supply

Removing and Replacing a Hot-Swappable Power Supply

Replacing a Hot-Swappable Power Supply

Replacing a Hot-Swappable Disk Drive Filler

Removing and Replacing a Hot-Swappable Disk Drive Filler

Removing and Replacing a Hot-Pluggable Disk Drive

Removing a Hot-Swappable Disk Drive Filler

Removing and Replacing a Hot-Pluggable Disk Drive

Disk Drive Load Order

Replacing a Hot-Pluggable Disk Drive

Removing and Replacing PCI/PCI-X/PCIe Card Dividers

Removing a PCI/PCI-X/PCIe Card Divider

Replacing a PCI/PCI-X/PCIe Card Divider

Removing and Replacing a Hot-Pluggable PCI/PCI-X/PCIe Card

Slot

PCI/PCI-X I/O Paths

PCI/PCI-X/PCIe Configurations

Slot Core I/O Board Slot

This section contains the following topics

PCI/PCI-X I/O Paths

VGA

PCI/PCI-X/PCIe I/O Paths

Shared Slots

Frequency3

Online Addition OLA

Online Replacement OLR

Replace the top cover. See Replacing the Top Cover

Removing a PCI/PCI-X/PCIe Card Offline

Installing a PCI/PCI-X/PCIe Card Offline

Removing the DVD Drive

Removing and Replacing the DVD Drive

Replacing the DVD Drive

Removing and Replacing the Memory Carrier Assembly

Removing the Memory Carrier Assembly

12 Removing and Replacing the Memory Carrier Assembly

Replacing the Memory Carrier Assembly

Removing System Memory

Removing and Replacing System Memory

13shows the memory carrier assembly removed from the chassis

14shows the memory carrier with the side cover removed

Optional, high-capacity Boards MB DIMMs

15 8-DIMM Memory Carrier Board Slot IDs

16 24-DIMM Memory Carrier Board Slot IDs

Installing Memory

Removing and Replacing the Memory Carrier Assembly

17 Inserting Dimm into Memory Board Connector

Removing the Front Bezel

Removing and Replacing the Front Bezel

18 Removing and Replacing the Front Bezel

Replacing the Front Bezel

Removing the Processor Board Assembly

Removing and Replacing the Processor Board Assembly

Removing and Replacing a Dual-Core Processor

Replacing the Processor Board Assembly

Processor Load Order

Required Tools

Removing a Dual-Core Processor

20 Processor Board Assembly

21shows the power connector and cable for the processor

22 Processor Alignment Posts and Lock/Unlock Mechanism

23 Processor Alignment Holes and Lock/Unlock Mechanism

Removing and Replacing Server Components

Removing the I/O Board Assembly

Removing and Replacing the I/O Board Assembly

Remove the top cover. See Removing the Top Cover

24 I/O Board Assembly

25 I/O Board Assembly Removal and Replacement

Replacing the I/O Board Assembly

Enable the TPM. See Replacing the TPM

Use the sysset command to verify that all values are set

Removing the System Battery

Removing and Replacing the System Battery

Core I/O Board Slot TPM System Battery

Replacing the System Battery

Removing the I/O VRM

Removing and Replacing the I/O Voltage Regulator Module

Replacing the I/O VRM

Removing and Replacing the Trusted Platform Module

Removing the TPM

28 TPM Location on I/O Board

Replacing the TPM

Removing and Replacing the Core I/O Board

Example 6-1 Enabling the TPM

VGA optional Server boards

Replacing the Core I/O Board

Removing the Core I/O Board

Removing and Replacing the Core I/O Board Battery

Removing the Core I/O Board Battery

Reconnect the USB cable to the card

Removing and Replacing the SAS Core I/O Card

Replacing the Core I/O Board Battery

Replacing the SAS Core I/O Card

Removing the SAS Core I/O Card

Reconnect the internal SAS cables to the card

Removing and Replacing the LAN Core I/O Card

Removing the LAN Core I/O Card

Replacing the LAN Core I/O Card

Removing the Display Board

Removing and Replacing the Display Board

Remove the DVD drive. See Removing the DVD Drive

30 Display Board Location

To replace the display board, follow these steps

Replacing the Display Board

Replace the DVD drive. See Replacing the DVD Drive

Removing and Replacing the SAS Backplane Board

Removing the SAS Backplane Board

33 Air Baffle Removal and Replacement

To replace the SAS backplane board, follow these steps

Replacing the SAS Backplane Board

Removing the Interconnect Board

Removing and Replacing the Interconnect Board

35 Interconnect Board Air Baffle

Lift the interconnect board out of the chassis Figure

Replacing the Interconnect Board

36 Interconnect Board Removal and Replacement

Removing and Replacing the Midplane Board

Removing the Midplane Board

To remove the midplane board, follow these steps

Remove the top cover. See Removing the Top Cover

37 Midplane Board

Replacing the Midplane Board

Replace the top cover. See Replacing the Top Cover

Parts Only Warranty Service

Customer Self Repair

Designated for your product

Customer Replaceable Units List

Customer Self Repair Information

Table A-2 CRU List

Fan Assemblies

Power Cords

Table B-1 Slot Speed Comparison and Planning Table

Backplane Upgrade

Backplane Upgrade Overview

This appendix address the following topics

Safety Information

Required Service Tools

Backplane Upgrade Procedure

Following is a checklist for upgrading the server

I/O Backplane Upgrade Checklist

Table B-2 I/O Backplane Upgrade Checklist

Backplane Upgrade

Removing the I/O Backplane

Information Bootable Devices

Table B-3 Cable kit part numbers

Installing Core I/O Cards

This chapter contains the following topics

Installing the HP Eight-Internal Port SAS Host Bus Adapter

Procedure B-2 Preparing the Server

Procedure B-3 Installing the Adapter Hardware

Procedure B-6 Preparing the Server

Installing the HP Smart Array P600

Procedure B-4 Connecting the Adapter to Other Devices

Procedure B-5 Completing the Adapter Installation

Procedure B-10 Preparing the Server

Installing the HP Smart Array P400

Procedure B-8 Connecting the Controller to Other Devices

Procedure B-9 Completing the Adapter Installation

Completing the Adapter Installation on HP-UX

Procedure B-12 Connecting the Controller to Other Devices

Procedure B-15 Updating the Firmware

Ready

Completing the Adapter Installation on Windows and Linux

Where Devicefile Controller device file Fwimage

Array Controller

Install the Integrity Support Pack

Installing the HP Smart Array P800

Windows Installation

Procedure B-17 Windows Quick Installation Procedure

Procedure B-19 Installing the controller board

Procedure B-21 Connecting to External Storage

Table B-4 SAS cable part numbers

Back up all data Close all applications

Linux Installation

Procedure B-23 Linux Quick Installation Procedure

Procedure B-24 Preparing the server

Procedure B-25 Installing the controller board

Procedure B-27 Connecting to External Storage

Table B-5 SAS cable part numbers

Novell Sles

Processor Upgrades

Upgrading Verses Adding On

Table B-6 Processor Upgrades

Operating systems

Firmware

282

Global Hot Spare

Integrated RAID

HP 8 Internal Port SAS HBA SAS Controller

Integrated Mirror

Flashing Firmware on First Controller

Table C-1 mptutil Commands and Functions

EFI Commands

Flashing Bios and EFI Driver on the First Controller

Common Questions About Flashing Firmware

Value

Figure C-2 Adapter Properties Screen

Limited

Currently supported type is IR.l

Figure C-3 Select New Array Type Screen

Field is grayed out under the following conditions

Too Small Disk is too small to mirror existing data

Size MB Displays the size of this array

Sized drives, excess space on larger drives are unusable

Figure C-4 SAS Topology Screen Expander Closed

Inquiry Data

Figure C-5 SAS Topology Screen Expander Open

Started

Elapsed Time

Scsi Device Type 0Eh Simplified Direct Access

Adapter for which to install a pre-OS IO interface

IO Timeouts

Scsi Device Type 00h Direct Access

Seconds

Other than

Controls LUN scans for the following devices

LUNs to Scan for Other Devices

Displays the PHY number current information

Expander Error

SMP Timeout

SMP CRC error

Has failed, since the last PHY Link Error Reset. a

Running Disparity Errors Number of dwords with running

Sequences, since the last PHY Link Error Reset. a

PHY Reset Errors Number of times the PHY reset sequence

Qsync

Delete

Controller #

Noprompt Eliminates warnings and prompts

Controller # SAS controller number between 0 Filename

SAS

Failed FLD

Progress

Inactive OKY

Its block size is incorrect, or its media is removable

Physical disk I/Os Quiesced or Not quiesced

Smart Array P400, P600 and P800 Controllers

Quick Installation Procedure

This command does not require controller #

Locate command turns locate LEDs on and off

Table C-2 SAS Cable Part Numbers

Connecting External Storage

Saupdate Utility

SAS Cable Part Numbers

Commands

Syntax

List

Help or ?

Update all

Ebsu Utility

Error Messages

Figure C-8 Ebsu Main Menu

Figure C-10 Ebsu Maintain Firmware Update Screen

Configuring the Array

Comparing the Utilities

Table C-3 ACU and Orca Supported Features and Procedures

Orca Utility

Creating a Logical Drive Using Orca

ACU Utility

316

Figure D-1 EFI Boot Sequence

Extensible Firmware Interface Boot Manager

Table D-1 EFI Commands

Table D-1lists EFI commands for the server

Cpuconfig

Operation

EFI/POSSE Commands

Help

Parameters

Example D-1 help command

Example D-2 help bch command

Example D-3 help configuration command

Example D-4 help cpuconfig command

Example D-5 help ioconfig command

Baud

Boottest

Example D-6 boottest command

Cpuconfig

Example D-10 conconfig command

Conconfig

Example D-8 cpuconfig command

Example D-9 cpuconfig 2 command

To change primary operating system console

Ioconfig

To disable a console

To enable a console

Default

Example D-14 ioconfig command

Errdump

Displays most system information

Info

System Information

Example D-15 info all command

Boot Information

Firmware Information

Example D-17 info mem command

Example D-16 info cpu command

Cdrom

Example D-18 info io command

None

Lanaddress

Monarch

Displays the core I/O MAC address

Pdt

Example D-21 monarch command

Sysmode

Example D-22 pdt command

Example D-23 pdt clear command

Displays or modifies the system mode

Using the Scsi Setup Utility

Example D-24 sysmode command

Specifying Scsi Parameters

Shell info io

Shell devtree

Shell drvcfg

Shell drvcfg -s drvrhandle cntrlhandle where

Shell reset

Table D-3 Server Sockets

Using the Boot Option Maintenance Menu

Boot From a File

Paths

Load Files The EFI Shell and the LAN

Add a Boot Option

Delete Boot Options

Change Boot Order

Manage BootNext Setting

Select Active Console Output Devices

Set Auto Boot TimeOut

Select Active Console Input Devices

Indicates a currently selected device

Table D-5 Console Output Devices

Resetting Passwords

Using the System Configuration Menu

Select Active Standard Error Devices

Security/Password Menu

ILO 2 MP

350

Index

Symbols

EFI

LAN

211

SAS

Index