28Chapter 1: Introduction to the EIU

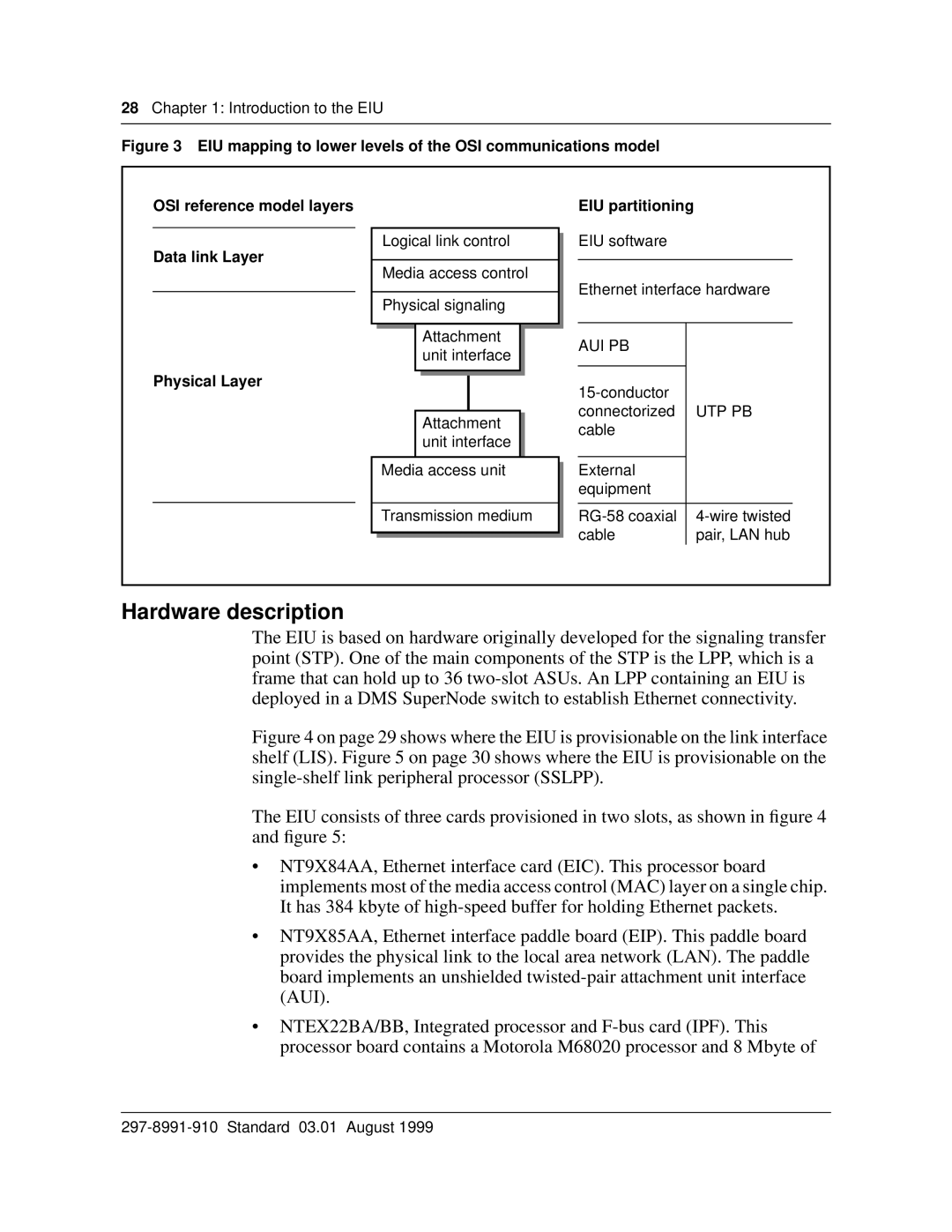

Figure 3 EIU mapping to lower levels of the OSI communications model

OSI reference model layers | EIU partitioning |

Data link Layer

Physical Layer

Logical link control

Media access control

Physical signaling

Attachment unit interface

Attachment unit interface

Media access unit

Transmission medium

EIU software

Ethernet interface hardware

AUI PB |

|

|

|

| |

connectorized | UTP PB |

cable |

|

|

|

External |

|

equipment |

|

|

|

cable | pair, LAN hub |

Hardware description

The EIU is based on hardware originally developed for the signaling transfer point (STP). One of the main components of the STP is the LPP, which is a frame that can hold up to 36